# **Dual H-Bridge Motor Driver**

# Features

- Dual H-Bridge Motor Driver With Current Control

1 or 2 DC Motors or 1 Stepper Motor

- Low On-Resistance:  $HS + LS = 1735m\Omega$ (Typical, 25°C)

- Output Current Capability (at V<sub>M</sub> = 5V, 25°C)

- TSSOP-16 (FD) Package

- 0.7A RMS, 1A Peak per H-Bridge

- 1.4A RMS in Parallel Mode

- TQFN3X3-16 and TQFN4X4-16 Package

- 0.6A RMS, 1A Peak per H-Bridge

- 1.2A RMS in Parallel Mode

- Wide Power Supply Voltage Range 2.7 to 10.8V

- Integrated Current Regulation

- Easy Pulse-Width-Modulation (PWM) Interface

- 1.6µA Low-Current Sleep Mode (at 5V)

- TSSOP-16 (FD), TQFN3X3-16 and TQFN4X4-16 Package

- ProtectionFeatures

- V<sub>M</sub> Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- Fault Indication Pin (nFAULT)

# Applications

- Point-of-Sale Printers

- Video Security Cameras

- Office Automation Machines

- Gaming Machines

- Robotics

- Battery-Powered Toys

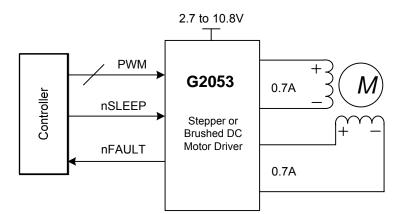

# **General Description**

The G2053 provides a dual-bridge motor driver solution for toys, printers, and other mechatronic applications.

The device has two H-bridges and can drive two DC brushed motors, a bipolar stepper motor, solenoids, or other inductive loads.

Each H-bridge output consists of a pair of N-channel and P-channel MOSFETs, with circuitry that regulates the winding current. With proper PCB design, each H-bridge of the G2053 can drive up to 700mA RMS (or DC) continuously, at 25°C with a V<sub>M</sub> supply of 5V. The device can support peak currents of up to 1 A per bridge. Current capability is reduced slightly at lower V<sub>M</sub> voltages.

Internal shutdown functions with a fault output pin are provided for overcurrent protection, short-circuit protection, UVLO, and overtemperature. A low-power sleep mode is also provided.

# **Ordering Information**

| ORDER<br>NUMBER | MARKING | TEMP.<br>RANGE | PACKAGE<br>(Green) |

|-----------------|---------|----------------|--------------------|

| G2053FC1U       | G2053   | -40°C to +85°C | TSSOP-16 (FD)      |

| G2053R41U       | 2053    | -40°C to +85°C | TQFN3X3-16         |

| G2053R81U       | 2053    | -40°C to +85°C | TQFN4X4-16         |

Note: FC: TSSOP-16 (FD) R4: TQFN3X3-16

R8: TQFN4X4-16

1: Bonding Code

U : Tape & Reel

Green: Lead Free / Halogen Free

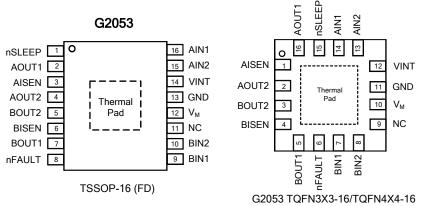

# **Pin Configuration**

Note: Recommend connecting the Thermal Pad to the Ground for excellent power dissipation.

# Absolute Maximum Ratings

| Ausolule Maximum Ralings                                              |

|-----------------------------------------------------------------------|

| Power supply $(V_M)$                                                  |

| Internal regulator (VINT)                                             |

| Control pins (AIN1, AIN2, BIN1, BIN2, nSLEEP,                         |

| nFAULT)                                                               |

| Continuous phase node pins (AOUT1, AOUT2, BOUT1,                      |

| BOUT2)                                                                |

| Pulsed 10µs phase node pins (AOUT1, AOUT2,                            |

| BOUT1, BOUT2)                                                         |

| Continuous shunt amplifier input pins (AISEN,                         |

| BISEN)                                                                |

| Pulsed 10µs shunt amplifier input pins (AISEN,                        |

| BISEN)1V to +1V                                                       |

| Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2,                       |

| AISEN, BISEN) Internally limited A                                    |

| Thermal Resistance of Junction to Ambient, ( $\theta$ <sub>JA</sub> ) |

| TSSOP-16 (FD)TBD°C/W                                                  |

| TQFN3X3-16                                                            |

| TQFN4X4-16                                                            |

| Continuous Power Dissipation ( $T_A = +25^{\circ}C$ )                 |

| TSSOP-16 (FD)TBDmW                                                    |

| TQFN3X3-16TBDmW                                                       |

| TQFN4X4-16TBDmW                                                       |

|                                                                       |

| Thermal Resistance of Junction to Ambient, ( $	heta$ <sub>JC</sub> )        |

|-----------------------------------------------------------------------------|

| TSSOP-16 (FD)TBD°C/W                                                        |

| TQFN3X3-16                                                                  |

| TQFN4X4-16                                                                  |

| Operating junction temperature $(T_J) \dots -40^{\circ}C$ to $150^{\circ}C$ |

| Storage Temperature (Tstg)65°C to 150°C                                     |

| Reflow Temperature (soldering, 10sec) 260°C                                 |

| ESD (HBM) ±2KV                                                              |

| ESD (CDM)                                                                   |

## **Recommended Operating Conditions**

| Power supply voltage $(V_M)^{(1)}$ 2.7V to 10        | .8V               |

|------------------------------------------------------|-------------------|

| Logic level input voltage (V <sub>1</sub> )0V to 5   | .5V               |

| Motor RMS current (I <sub>RMS</sub> ) <sup>(2)</sup> |                   |

| TSSOP-16 (FD)0 to 0                                  | .7A               |

| TQFN3X3-16/TQFN4X4-16 0 to 0                         | .6A               |

| Applied PWM signal to AIN1, AIN2, BIN1, or B         | IN2               |

| (f <sub>PWM</sub> )                                  | <hz< td=""></hz<> |

| Operating ambient temperature $(T_A)$ 40°C to 88     | 5°C               |

Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(1) Note that when  $V_M$  is below 5V,  $R_{DS(ON)}$  increases and maximum output current is reduced.

(2) Power dissipation and thermal limits must be observed.

# **Electrical Characteristics**

#### (T<sub>A</sub>=25°C)

The device is not guaranteed to function outside its operating conditions. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified.

| PARAMETER                               | SYMBOL             | CONDITIONS                           | MIN | TYP | MAX  | UNIT |  |

|-----------------------------------------|--------------------|--------------------------------------|-----|-----|------|------|--|

| POWER SUPPLIES (V <sub>M</sub> , VINT)  |                    |                                      |     |     |      |      |  |

| V <sub>M</sub> operating voltage        | V <sub>M</sub>     |                                      | 2.7 |     | 10.8 | V    |  |

| V <sub>M</sub> operating supply current | I <sub>VM</sub>    | $V_{M}$ = 5V, xINx low, nSLEEP high  |     | 1.7 | 3    | mA   |  |

| $V_M$ sleep mode supply current         | I <sub>VMQ</sub>   | V <sub>M</sub> = 5V, nSLEEP low 1.6  |     | 1.6 | 2.7  | μA   |  |

| Sleep time                              | t <sub>SLEEP</sub> | nSLEEP low to sleep mode             |     | 10  |      | μs   |  |

| Wake-up time                            | twake              | nSLEEP high to output transition     |     | 155 |      | μs   |  |

| Turn-on time                            | t <sub>on</sub>    | $V_{M}$ > VUVLO to output transition |     | 25  |      | μs   |  |

| Internal regulator voltage              | V <sub>INT</sub>   | $V_{M}$ > VUVLO to output transition | 3   | 3.3 | 3.6  | V    |  |

| CONTROL INPUTS (AIN1, AIN2, BIN1, BI    | N2, nSLEEP         | )                                    |     |     | -    |      |  |

| Input logic low voltage                 | V                  | xINx 0                               |     | 0.7 | V    |      |  |

| Input logic low voltage                 | VIL                | V <sub>IL</sub> nSLEEP               |     |     |      | 0.5  |  |

| Innut Ionia high voltage                | V                  | V <sub>IH</sub> xINx<br>nSLEEP       |     |     | 5.5  | V    |  |

| Input logic high voltage                | VIH                |                                      |     |     | 5.5  |      |  |

| Input logic hysteresis                  | V <sub>HYS</sub>   |                                      | 350 | 400 | 650  | mV   |  |

| Input logic low current                 | IIL                | VIN = 0V                             | -1  |     | 1    | μA   |  |

| Input logic high current                | I <sub>IH</sub>    | VIN = 5V                             |     |     | 50   | μA   |  |

|                                         |                    | xINx                                 | 100 | 150 | 250  | ko   |  |

| Pulldown resistance                     | R <sub>PD</sub>    | nSLEEP                               | 380 | 500 | 750  | kΩ   |  |

| Input deglitch time                     | t <sub>DEG</sub>   |                                      |     | 575 |      | ns   |  |

| Propagation delay INx to OUTx           | t <sub>PROP</sub>  | $V_{IN} = 5V$                        |     | 1.2 |      | μs   |  |

# Electrical Characteristics (Continued)

| PARAMETER                                         | SYMBOL                          | CONDITIONS                                             | MIN | TYP  | MAX | UNIT |  |  |

|---------------------------------------------------|---------------------------------|--------------------------------------------------------|-----|------|-----|------|--|--|

| CONTROL OUTPUTS (nFAULT)                          |                                 |                                                        | _   | _    |     |      |  |  |

| Output logic low voltage                          | V <sub>OL</sub>                 | I <sub>O</sub> = 5mA                                   |     |      | 0.5 | V    |  |  |

| Output logic high leakage                         | I <sub>OH</sub>                 | $R_{PULLUP} = 1k\Omega$ to 5V                          | -1  |      | 1   | μA   |  |  |

| MOTOR DRIVER OUTPUTS (AOUT1, AOUT2, BOUT1, BOUT2) |                                 |                                                        |     |      |     |      |  |  |

|                                                   |                                 | V <sub>M</sub> = 5V, I = 0.2A, T <sub>A</sub> = 25°C   |     | 817  |     |      |  |  |

| High-side FET on-resistance                       | R <sub>DS(ON)</sub>             | V <sub>M</sub> = 2.7V, I = 0.2A, T <sub>A</sub> = 25°C |     | 1140 |     | mΩ   |  |  |

|                                                   |                                 | V <sub>M</sub> = 5V, I = 0.2A, T <sub>A</sub> = 25°C   |     | 285  |     |      |  |  |

| Low-side FET on-resistance                        | R <sub>DS(ON)</sub>             | $R_{DS(ON)} = 2.7V, I = 0.2A, T_A = 25^{\circ}C$       |     | 382  |     | mΩ   |  |  |

| Off-state leakage current                         | IOFF                            | V <sub>M</sub> = 5V                                    | -1  |      | 1   | μA   |  |  |

| Output rise time                                  | t <sub>RISE</sub>               | $V_M$ = 5V; $R_L$ = 16 $\Omega$ to GND                 |     | 70   |     | ns   |  |  |

| Output fall time                                  | t <sub>FALL</sub>               | $V_M$ = 5V; $R_L$ = 16 $\Omega$ to VM                  |     | 80   |     | ns   |  |  |

| Output dead time                                  | t <sub>DEAD</sub>               | Internal dead time                                     |     | 450  |     | ns   |  |  |

| PWM CURRENT CONTROL (AISEN, BISI                  | EN)                             |                                                        | •   | -    |     |      |  |  |

| xISEN trip voltage                                | V <sub>TRIP</sub>               |                                                        | 160 | 200  | 240 | mV   |  |  |

| Current control constant off time                 | t <sub>OFF</sub>                | Internal PWM constant off time                         |     | 20   |     | μs   |  |  |

| PROTECTION CIRCUITS                               | <u>.</u>                        |                                                        | •   | -    |     |      |  |  |

|                                                   | N/                              | V <sub>M</sub> falling; UVLO report                    |     |      | 2.6 | v    |  |  |

| V <sub>M</sub> undervoltage lockout               | V <sub>UVLO</sub>               | V <sub>M</sub> rising; UVLO recovery                   |     |      | 2.7 | v    |  |  |

| V <sub>M</sub> undervoltage hysteresis            | V <sub>UVLO,HYS</sub>           | Rising to falling threshold                            |     | 90   |     | mV   |  |  |

| Overcurrent protection trip level                 | I <sub>OCP</sub>                |                                                        | 1   |      |     | А    |  |  |

| Overcurrent deglitch time                         | t <sub>DEG</sub>                |                                                        |     | 2.3  |     | μs   |  |  |

| Overcurrent protection period                     | t <sub>OCP</sub>                |                                                        |     | 1.4  |     | ms   |  |  |

| Thermal shutdown temperature                      | T <sub>TSD</sub> <sup>(1)</sup> | Die temperature, TJ                                    | 150 |      |     | °C   |  |  |

| Thermal shutdown hysteresis                       | T <sub>HYS</sub>                | Die temperature, T                                     |     | 20   |     | °C   |  |  |

# Pin Description

| NAME   | PI    | N    | TYPE | FUNCTION                   |                                                                                                     |  |  |  |  |

|--------|-------|------|------|----------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| NAWE   | TSSOP | TQFN | ITPE |                            |                                                                                                     |  |  |  |  |

| POWER  |       | OUND |      |                            |                                                                                                     |  |  |  |  |

| GND    | 13    | 11   | PWR  | Device ground              | Both the GND pin and device PowerPAD must be connected to ground                                    |  |  |  |  |

| VINT   | 14    | 12   | -    | Internal regulator (3.3 V) | Internal supply voltage; bypass to GND with 2.2µF, 6.3V capacitor                                   |  |  |  |  |

| Vм     | 12    | 10   | PWR  | Power supply               | Connect to motor supply voltage; bypass to GND with a $10\mu F$ (minimum) capacitor rated for $V_M$ |  |  |  |  |

| CONTRO | )L    |      |      |                            |                                                                                                     |  |  |  |  |

| AIN1   | 16    | 14   |      | Li heidere A DIA/AA issed  |                                                                                                     |  |  |  |  |

| AIN2   | 15    | 13   | Ι    | H-bridge A PWM input       | Controls the state of AOUT1 and AOUT2; internal pulldown                                            |  |  |  |  |

| BIN1   | 9     | 7    | -    | Li bridge D D\A/M input    | Controls the state of DOUT4 and DOUT9; internal multideum                                           |  |  |  |  |

| BIN2   | 10    | 8    | I    | H-bridge B PWM input       | Controls the state of BOUT1 and BOUT2; internal pulldown                                            |  |  |  |  |

| nSLEEP | 1     | 15   | Ι    | Sleep mode input           | Logic high to enable device; logic low to enter low-power sleep mode;<br>internal pulldown          |  |  |  |  |

| STATUS |       |      |      |                            |                                                                                                     |  |  |  |  |

| nFAULT | 8     | 6    | OD   | Fault indication pin       | Pulled logic low with fault condition; open-drain output requires an ex-<br>ternal pullup           |  |  |  |  |

| OUTPUT |       |      |      |                            |                                                                                                     |  |  |  |  |

| AISEN  | 3     | 1    | 0    | Bridge A sense             | Sense resistor to GND sets PWM current regulation level (see <i>PWM Motor Drivers)</i>              |  |  |  |  |

| AOUT1  | 2     | 16   | 0    | Dridera A autout           |                                                                                                     |  |  |  |  |

| AOUT2  | 4     | 2    | 0    | Bridge A output            | Positive current is AOUT1 $\rightarrow$ AOUT2                                                       |  |  |  |  |

| BISEN  | 6     | 4    | 0    | Bridge B sense             | Sense resistor to GND sets PWM current regulation level (see <i>PWM Motor Drivers</i> )             |  |  |  |  |

| BOUT1  | 7     |      |      |                            |                                                                                                     |  |  |  |  |

| BOUT2  | 5     | 3    | 0    | Bridge B output            | Positive current is BOUT1 $\rightarrow$ BOUT2                                                       |  |  |  |  |

#### Detailed Description Overview

The G2053 device is an integrated motor driver solution for brushed DC or bipolar stepper motors. The device integrates two PMOS + NMOS H-bridges and current regulation circuitry. The G2053 can be powered with a supply voltage from 2.7 to 10.8V and can provide an output current up to 700mA RMS.

A simple PWM interface allows easy interfacing to the controller circuit.

The current regulation is a 20µs fixed off-time slow decay.

The device includes a low-power sleep mode, which lets the system save power when not driving the motor.

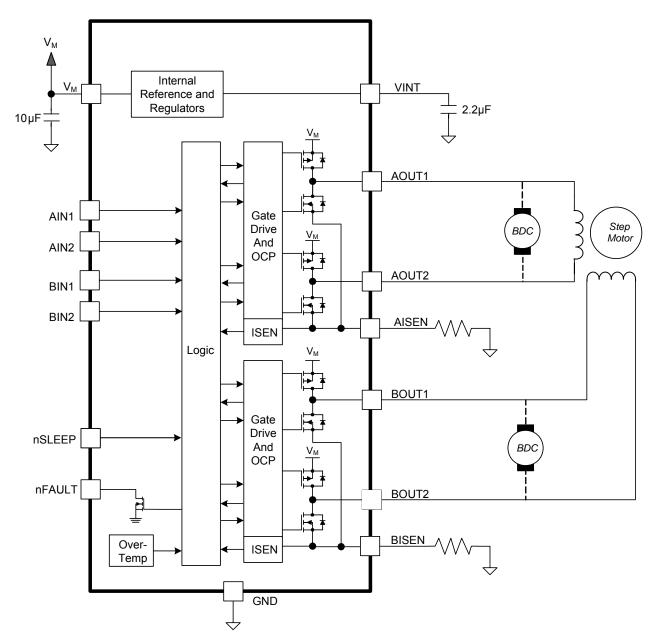

#### Functional Block Diagram

# Feature Description

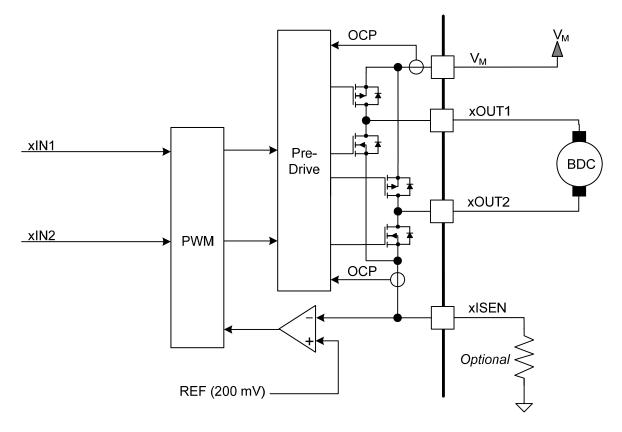

### **PWM Motor Drivers**

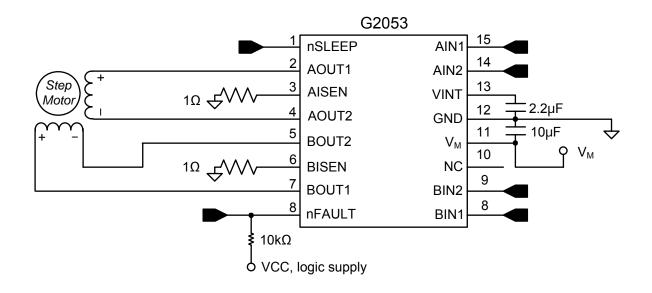

The G2053 contains drivers for two full H-bridges. Figure 6 shows a block diagram of the circuitry.

Figure 6. H-Bridge and Current-Chopping Circuitry

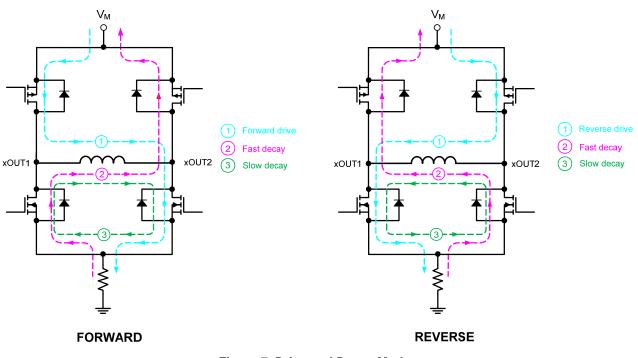

### Bridge Control and Decay Modes

The AIN1 and AIN2 input pins control the state of the AOUT1 and AOUT2 outputs; similarly, the BIN1 and BIN2 input pins control the state of the BOUT1 and BOUT2 outputs (see Table 1).

| xIN1 | xIN2 | xOUT1 | xOUT2 | FUNCTION           |

|------|------|-------|-------|--------------------|

| 0    | 0    | Z     | Z     | Coast / fast decay |

| 0    | 1    | L     | Н     | Reverse            |

| 1    | 0    | Н     | L     | Forward            |

| 1    | 1    | L     | L     | Brake / slow decay |

The inputs can also be used for PWM control of the motor speed. When controlling a winding with PWM and the drive current is interrupted, the inductive nature of the motor requires that the current must continue to flow (called recirculation current). To handle this recirculation current, the H-bridge can operate in two different states, fast decay or slow decay. In fast-decay mode, the H-bridge is disabled and recirculation current flows through the body diodes. In slow-decay mode, the motor winding is shorted by enabling both low-side FETs.

To externally pulse-width modulate the bridge in fast-decay mode, the PWM signal is applied to one xIN pin while the other is held low; to use slow-decay mode, one xIN pin is held high. See Table 2 for more information.

| xIN1 | xIN2 | FUNCTION                |

|------|------|-------------------------|

| PWM  | 0    | Forward PWM, fast decay |

| 1    | PWM  | Forward PWM, slow decay |

| 0    | PWM  | Reverse PWM, fast decay |

| PWM  | 1    | Reverse PWM, slow decay |

Table 2. PWM Control of Motor Speed

The internal current control is still enabled when applying external PWM to xIN. To disable the current control when applying external PWM, the xISEN pins should be connected directly to ground. Figure 7 show the current paths in different drive and decay modes.

Figure 7. Drive and Decay Modes

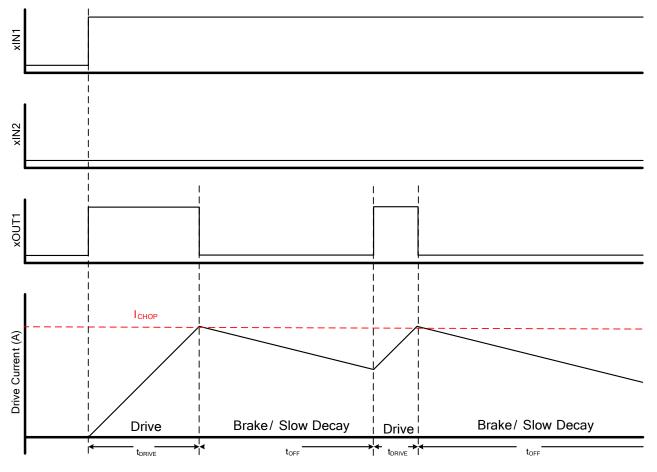

### Current Control

The current through the motor windings may be limited, or controlled, by a 20µs constant off-time PWM current regulation, or current chopping. For DC motors, current control is used to limit the start-up and stall current of the motor. For stepper motors, current control is often used at all times.

When an H-bridge is enabled, current rises through the winding at a rate dependent on the DC voltage and inductance of the winding. If the current reaches the current chopping threshold, the bridge disables the current until the beginning of the next PWM cycle. Note that immediately after the output is enabled, the voltage on the xISEN pin is ignored for a fixed period of time before enabling the current sense circuitry. This blanking time is fixed at 3.75µs.

The PWM chopping current is set by a comparator that compares the voltage across a current sense resistor

connected to the xISEN pins with a reference voltage. The reference voltage,  $V_{TRIP}$ , is is fixed at 200mV nominally.

The chopping current is calculated as in Equation 1.

$$I_{CHOP} = \frac{200mV}{R_{XISEN}}$$

(1)

Example: If a 1 $\Omega$  sense resistor is used, the chopping current will be 200 mV / 1 $\Omega$  = 200mA.

#### Decay Mode

After the chopping current threshold is reached, the H-bridge switches to slow-decay mode. This state is held for  $t_{off}$  (20µs) until the next cycle to turn on the high-side MOSFETs.

#### Slow Decay

In slow-decay mode, the high-side MOSFETs are turned off and both of the low-side MOSFETs are turned on. The motor current decreases while flowing in the two low-side MOSFETs until reaching its fixed off time (typically 20µs). After that, the high-side MOSFETs are enabled to increase the winding current again.

#### Sleep Mode

Driving nSLEEP low puts the device into a low-power sleep state. In this state, the H-bridges are disabled, all internal logic is reset, and all internal clocks are stopped. All inputs are ignored until nSLEEP returns inactive high. When returning from sleep mode, some time,  $t_{WAKE}$ , needs to pass before the motor driver becomes fully operational. To make the board design simple, the nSLEEP can be pulled up to the supply (V<sub>M</sub>). GMT recommends to use a pullup resistor when this is done. This resistor limits the current to the input in case V<sub>M</sub> is higher than 6.5V. Internally, the nSLEEP pin has a 500k $\Omega$  resistor to GND. It also has a clamping Zener diode that clamps the voltage at the pin at 6.5V. Currents greater than 250µA can cause damage to the input structure. Therefore, GMT recommends a pullup resistor between 20 to 75k $\Omega$ .

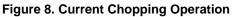

#### Parallel Mode

The two H-bridges in the G2053 can be connected in parallel for double the current of a single H-bridge. The internal dead time in the G2053 prevents any risk of cross-conduction (shoot-through) between the two bridges due to timing differences between the two bridges. Figure 9 shows the connections.

Figure 9. Parallel Mode Schematic

#### **Protection Circuits**

The G2053 is fully protected against overcurrent, overtemperature, and undervoltage events.

#### **Overcurrent Protection (OCP)**

An analog current limit ( $I_{OCP}$ ) circuit on each FET limits the current through the FET by limiting the gate drive. If this analog current limit persists for longer than the OCP deglitch time ( $t_{DEG}$ ), all FETs in the H-bridge are disabled and the nFAULT pin is driven low. The driver is re-enabled after the OCP retry period ( $t_{OCP}$ ) has passed. nFAULT becomes high again after the retry time. If the fault condition is still present, the cycle repeats. If the fault is no longer present, normal operation resumes and nFAULT remains deasserted. Note that only the H-bridge in which the OCP is detected will be disabled while the other bridge functions normally.

Overcurrent conditions are detected independently on both high-side and low-side devices; a short to ground, supply, or across the motor winding all result in an overcurrent shutdown. Note that overcurrent protection does not use the current sense circuitry used for PWM current control, so it functions even without presence of the xISEN resistors.

#### **Thermal Shutdown (TSD)**

If the die temperature exceeds safe limits, all FETs in the H-bridge are disabled and the nFAULT pin is driven low. After the die temperature has fallen below the specified hysteresis ( $T_{HYS}$ ), operation automatically resumes. The nFAULT pin is released after operation has resumed.

#### UVLO

If at any time the voltage on the  $V_M$  pin falls below the UVLO threshold voltage,  $V_{UVLO}$ , all circuitry in the device is disabled, and all internal logic is reset. Operation resumes when  $V_M$  rises above the UVLO threshold. The nFAULT pin is not driven low during an undervoltage condition.

#### Table 3. Device Protection

| Fault                              | Condition                           | Error Report | H-Bridge | Internal Circuits | Recovery                  |

|------------------------------------|-------------------------------------|--------------|----------|-------------------|---------------------------|

| V <sub>M</sub> undervoltage (UVLO) | V <sub>M</sub> < 2.6 V              | None         | Disabled | Disabled          | V <sub>M</sub> > 2.7 V    |

| Overcurrent (OCP)                  | I <sub>OUT</sub> > I <sub>OCP</sub> | FAULTn       | Disabled | Operating         | OCP                       |

| Thermal Shutdown (TSD)             | $T_J > T_{TSD}$                     | FAULTn       | Disabled | Operating         | $T_J < T_{TSD} - T_{HYS}$ |

#### **Device Functional Modes**

The G2053 is active unless the nSLEEP pin is brought logic low. In sleep mode, the H-bridge FETs are

disabled (Hi-Z). Note that  $t_{SLEEP}$  must elapse after a falling edge on the nSLEEP pin before the device is in sleep mode. The G2053 is brought out of sleep mode automatically if nSLEEP is brought logic high. Note that  $t_{WAKE}$  must elapse before the outputs change state after wake-up.

#### Table 4. Modes of Operation

| Fault             | Condition               | H-Bridge  | Internal Circuits |

|-------------------|-------------------------|-----------|-------------------|

| Operating         | nSLEEP pin high         | Operating | Operating         |

| Sleep mode        | nSLEEP pin low          | Disabled  | Disabled          |

| Fault encountered | Any fault condition met | Disabled  | See Table 3       |

### Application and Implementation Application Information

The G2053 is used in stepper or brushed DC motor control. The following design procedure can be used to configure the G2053 in a bipolar stepper motor application.

# **Typical Application**

#### Design Requirements

Table 5 gives design input parameters for system design.

| Design Parameter         | Reference         | Example Value     |  |

|--------------------------|-------------------|-------------------|--|

| Supply voltage           | V <sub>M</sub>    | 9 V               |  |

| Motor winding resistance | RL                | $12\Omega/phase$  |  |

| Motor winding inductance | LL                | 10 mH/phase       |  |

| Motor full step angle    | $\theta_{step}$   | 1.8 °/step        |  |

| Target stepping level    | n <sub>m</sub>    | 2 (half-stepping) |  |

| Target motor speed       | V                 | 120 rpm           |  |

| Target chopping current  | I <sub>CHOP</sub> | 200 mA            |  |

| Sense resistor           | RISEN             | 1Ω                |  |

Table 5. Design Parameters

#### **Detailed Design Procedure**

#### **Stepper Motor Speed**

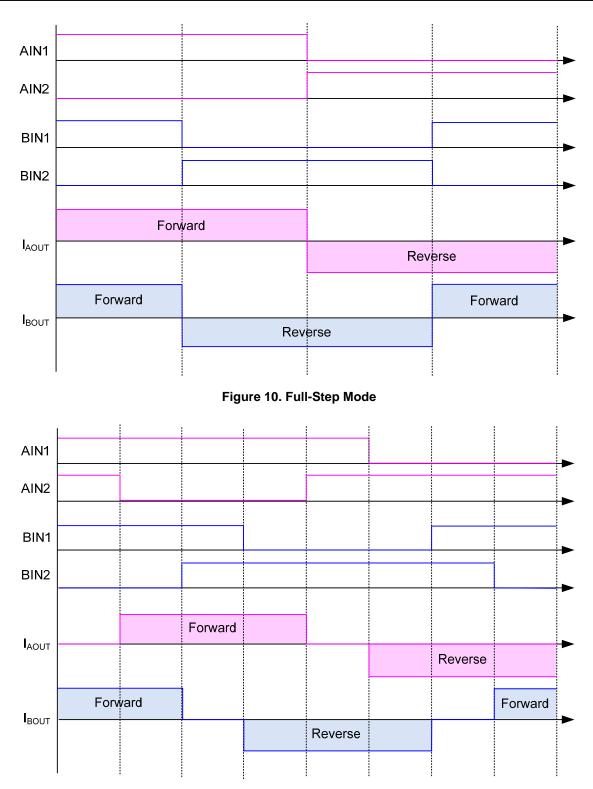

The first step in configuring the G2053 requires the desired motor speed and stepping level. The G2053 can support full- and half-stepping modes using the PWM interface.

If the target motor speed is too high, the motor does not spin. Ensure that the motor can support the target speed.

For a desired motor speed (v), microstepping level ( $n_m$ ), and motor full step angle ( $\theta_{step}$ ),

$f_{step}(step / s) = \frac{v(rpm)xn_m(steps)x360^{\circ} / rot}{Q_{step}(^{\circ} / step)x60s / min}$

(2)

#### Figure 11. Half-Step Mode

#### **Current Regulation**

The chopping current ( $I_{CHOP}$ ) is the maximum current driven through either winding. This quantity depends on the sense resistor value ( $R_{XISEN}$ ).

$$I_{CHOP} = \frac{200mV}{R_{XISEN}}$$

(3)

$I_{CHOP}$  is set by a comparator which compares the voltage across  $R_{XISEN}$  to a reference voltage. Note that  $I_{CHOP}$  must follow Equation 4 to avoid saturating the motor.

$$I_{FS}(A) < \frac{V_{M}(V)}{R_{L}(\Omega) + R_{DS(ON)}HS(\Omega) + R_{DS(ON)}LS(\Omega)}$$

(4)

(4)

Where

- V<sub>M</sub> is the motor supply voltage.

- R<sub>L</sub> is the motor winding resistance

#### **Power Supply Recommendations**

The G2053 is designed to operate from an input voltage supply ( $V_M$ ) range between 2.7 to 10.8V. A 10 $\mu$ F ceramic capacitor rated for  $V_M$  must be placed as close to the G2053 as possible.

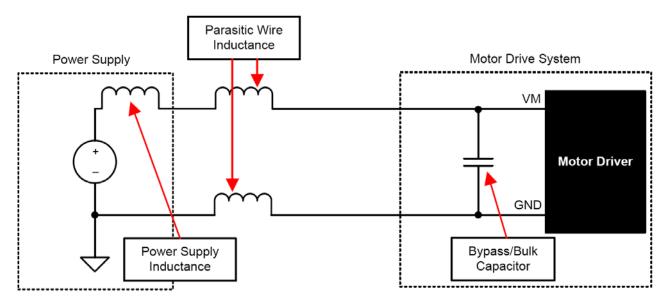

#### Sizing Bulk Capacitance for Motor Drive Systems

Bulk capacitance sizing is an important factor in motor drive system design. It depends on a variety of factors including:

- Type of power supply

- Acceptable supply voltage ripple

- Parasitic inductance in the power supply wiring

- Type of motor (brushed DC, brushless DC, stepper)

- Motor startup current

- Motor braking method

The inductance between the power supply and motor drive system limits the rate current can change from the power supply. If the local bulk capacitance is too small, the system responds to excessive current demands or dumps from the motor with a change in voltage. Size the bulk capacitance to meet acceptable voltage ripple levels.

The data sheet generally provides a recommended value, but system-level testing is required to determine the appropriate-sized bulk capacitor.

Figure 13. Setup of Motor Drive System With External Power Supply

### Layout Guidelines

Bypass the V<sub>M</sub> terminal to GND using a low-ESR ceramic bypass capacitor with a recommended value of  $10\mu$ F rated for V<sub>M</sub>. This capacitor should be placed as close to the V<sub>M</sub> pin as possible with a thick trace or ground plane connection to the device GND pin and PowerPAD.

Bypass VINT to ground with a ceramic capacitor rated 6.3V. Place this bypassing capacitor as close to the pin as possible.

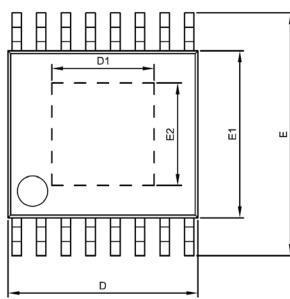

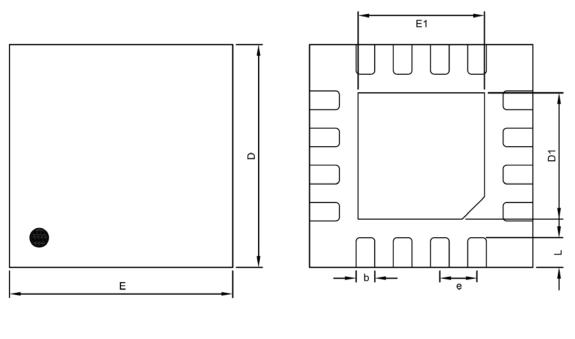

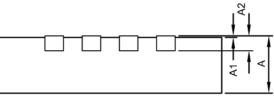

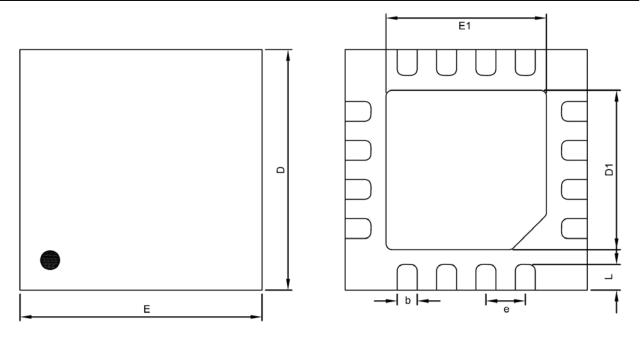

# Package Information

TSSOP-16 (FD) Package

| Gumbal | DIMENSION IN MM |          |      | DIMENSION IN INCH |           |       |

|--------|-----------------|----------|------|-------------------|-----------|-------|

| Symbol | MIN.            | NOM.     | MAX. | MIN.              | NOM.      | MAX.  |

| A      |                 |          | 1.20 |                   |           | 0.048 |

| A1     | 0.00            |          | 0.15 | 0.000             |           | 0.006 |

| A2     | 0.80            | 1.00     | 1.05 | 0.033             | 0.039     | 0.041 |

| D      | 4.90            | 5.00     | 5.10 | 0.193             | 0.197     | 0.201 |

| E      | 6.20            | 6.40     | 6.60 | 0.244             | 0.252     | 0.260 |

| E1     | 4.30            | 4.40     | 4.50 | 0.169             | 0.173     | 0.177 |

| D1     | 2.40            | 2.70     | 3.00 | 0.094             | 0.106     | 0.118 |

| E2     | 2.40            | 2.70     | 3.00 | 0.094             | 0.106     | 0.118 |

| с      | 0.09            |          | 0.20 | 0.004             |           | 0.008 |

| b      | 0.19            | 0.22     | 0.30 | 0.008             | 0.009     | 0.012 |

| е      |                 | 0.65 BSC |      |                   | 0.026 BSC |       |

| L      | 0.45            | 0.60     | 0.75 | 0.018             | 0.024     | 0.030 |

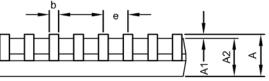

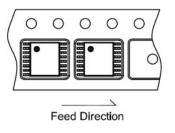

# **Taping Specification**

| PACKAGE       | Q'TY/BY REEL |

|---------------|--------------|

| TSSOP-16 (FD) | 3,000 ea     |

TQFN3X3-16 Package

| 0hal   | DIMENSION IN MM |          |            | DIMENSION IN INCH |            |        |

|--------|-----------------|----------|------------|-------------------|------------|--------|

| Symbol | MIN.            | NOM.     | MAX.       | MIN.              | NOM.       | MAX.   |

| A      | 0.70            | 0.75     | 0.80       | 0.0276            | 0.0295     | 0.0315 |

| A1     | 0.00            |          | 0.05       | 0.0000            |            | 0.0020 |

| A2     | 0.20 REF        |          | 0.0079 REF |                   |            |        |

| D      | 2.95            | 3.00     | 3.05       | 0.1161            | 0.1181     | 0.1201 |

| E      | 2.95            | 3.00     | 3.05       | 0.1161            | 0.1181     | 0.1201 |

| D1     | 1.60            | 1.70     | 1.80       | 0.0630            | 0.0669     | 0.0689 |

| E1     | 1.60            | 1.70     | 1.80       | 0.0630            | 0.0669     | 0.0689 |

| b      | 0,18            | 0,25     | 0.30       | 0.0071            | 0.0098     | 0.0118 |

| е      |                 | 0.50 BSC |            |                   | 0.0197 BSC |        |

| L      | 0.35            | 0.40     | 0.45       | 0.0138            | 0.0157     | 0.0177 |

# **Taping Specification**

| PACKAGE    | Q'TY/BY REEL |

|------------|--------------|

| TQFN3X3-16 | 3,000 ea     |

TQFN4X4-16 Package

| Combal | DIMENSION IN MM |      |            | DIMENSION IN INCH |        |        |

|--------|-----------------|------|------------|-------------------|--------|--------|

| Symbol | MIN.            | NOM. | MAX.       | MIN.              | NOM.   | MAX.   |

| A      | 0.70            | 0.75 | 0.80       | 0.0276            | 0.0295 | 0.0315 |

| A1     | 0.00            |      | 0.05       | 0.0000            |        | 0.0020 |

| A2     | 0.20 REF        |      |            | 0.0079 REF        |        |        |

| D      | 3.95            | 4.00 | 4.05       | 0.1555            | 0.1575 | 0.1594 |

| E      | 3.95            | 4.00 | 4.05       | 0.1555            | 0.1575 | 0.1594 |

| D1     | 2.50            | 2.60 | 2.70       | 0.0984            | 0.1024 | 0.1063 |

| E1     | 2.50            | 2.60 | 2.70       | 0.0984            | 0.1024 | 0.1063 |

| b      | 0.25            | 0.30 | 0.38       | 0.0098            | 0.0118 | 0.0150 |

| e      | 0.65 BSC        |      | 0.0256 BSC |                   |        |        |

| L      | 0.30            | 0.40 | 0.45       | 0.0118            | 0.0157 | 0.0177 |

# **Taping Specification**

| PACKAGE    | Q'TY/BY REEL |

|------------|--------------|

| TQFN4X4-16 | 3,000 ea     |

GMT Inc. does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and GMT Inc. reserves the right at any time without notice to change said circuitry and specifications.