## **3A Ultra-Small Low Ron and Controlled Load Switch with Auto-Discharge Path**

# **NCP451**

The NCP451 is a very low Ron MOSFET controlled by external logic pin, allowing optimization of battery life, and portable device autonomy.

Indeed, due to a current consumption optimization with NMOS structure, leakage currents are eliminated by isolating connected IC on the battery when not used.

Output discharge path is also embedded to eliminate residual voltages on the output rail.

Proposed in a wide input voltage range from 0.75 V to 5.5 V, in a small 0.9 x 1.4 mm WLCSP6, pitch 0.5 mm.

#### Features

- 0.75 V 5.5 V Operating Range

- $12 \text{ m}\Omega \text{ N}$  MOSFET from 3.6 V to 5.5 V

- 13 m $\Omega$  N MOSFET from 1 V to 3.3 V

- DC Current Up to 3 A

- Output Auto–Discharge

- Active High EN Pin

- WLCSP6 0.9 x 1.4 mm

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- Mobile Phones

- Tablets

- Digital Cameras

- GPS

- Portable Devices

XXXX = Specific Device Code

- A = Assembly Location

- Y = Year

- W = Work Week

- = Pb-Free Package

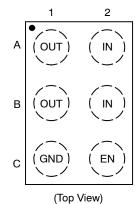

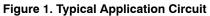

#### **PINOUT DIAGRAM**

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 10 of this data sheet.

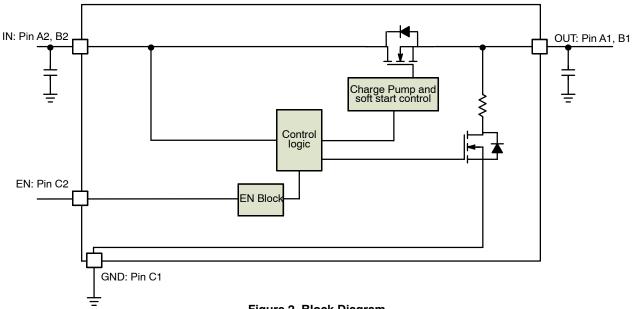

### **PIN FUNCTION DESCRIPTION**

| Pin Name | Pin Number | Туре   | Description                                                                                                                    |

|----------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| IN       | A2, B2     | POWER  | Load-switch input voltage; connect a 1 $\mu F$ or greater ceramic capacitor from IN to GND as close as possible to the IC.     |

| GND      | C1         | POWER  | Ground connection.                                                                                                             |

| EN       | C2         | INPUT  | Enable input, logic high turns on power switch.                                                                                |

| OUT      | A1, B1     | OUTPUT | Load–switch output; connect a 1 $\mu\text{F}$ ceramic capacitor from OUT to GND as close as possible to the IC is recommended. |

### **BLOCK DIAGRAM**

#### MAXIMUM RATINGS

| Symbol                                                   | Rating                                                | Value         | Unit |

|----------------------------------------------------------|-------------------------------------------------------|---------------|------|

| IN, OUT, EN, Pins: (Note 1)                              | V <sub>EN,</sub> V <sub>IN,</sub><br>V <sub>OUT</sub> | -0.3 to + 7.0 | V    |

| From IN to OUT Pins: Input/Output (Note 1)               | V <sub>IN,</sub> V <sub>OUT</sub>                     | 0 to + 7.0    | V    |

| Human Body Model (HBM) ESD Rating are (Notes 1 and 2)    | ESD HBM                                               | 1.5           | kV   |

| Machine Model (MM) ESD Rating are (Notes 1 and 2)        | ESD MM                                                | 250           | V    |

| Charge Device Model (CDM) ESD Rating are (Notes 1 and 2) | ESD CDM                                               | 2000          | V    |

| Latch-up protection (Note 3)<br>-Pins IN, OUT, EN        | LU                                                    | 100           | mA   |

| Maximum Junction Temperature                             | TJ                                                    | -40 to + 125  | °C   |

| Storage Temperature Range                                | T <sub>STG</sub>                                      | -40 to + 150  | °C   |

| Moisture Sensitivity (Note 4)                            | MSL                                                   | Level 1       |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. According to JEDEC standard JESD22-A108.

This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ±1.5 kV per JEDEC standard: JESD22–A114 for all pins. Machine Model (MM) ±250 V per JEDEC standard: JESD22–A115 for all pins. Charge Device Model (CDM) ±2.0 kV per JEDEC standard: JESD22–C101 for all pins.

Latchup Current Maximum Rating: ±100 mA per JEDEC standard: JESD78 class II.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J–STD–020.

#### **OPERATING CONDITIONS**

| Symbol           | Parameter                          | Conditions       | Min  | Тур   | Max  | Unit |

|------------------|------------------------------------|------------------|------|-------|------|------|

| V <sub>IN</sub>  | Operational Power Supply           |                  | 0.75 |       | 5.5  | V    |

| V <sub>EN</sub>  | Enable Voltage                     |                  | 0    |       | 5.5  | V    |

| T <sub>A</sub>   | Ambient Temperature Range          |                  | -40  | 25    | +85  | °C   |

| TJ               | Junction Temperature Range         |                  | -40  | 25    | +125 | °C   |

| C <sub>IN</sub>  | Decoupling input capacitor         |                  | 1    |       |      | μF   |

| C <sub>OUT</sub> | Decoupling output capacitor        |                  | 0.1  |       |      | μF   |

| $R_{\theta JA}$  | Thermal Resistance Junction to Air | (Note 5)         |      | 100   |      | °C/W |

| I <sub>OUT</sub> | Maximum DC current                 |                  |      |       | 3    | А    |

| PD               | Power Dissipation Rating (Note 6)  | Over temperature |      | 0.315 |      | W    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability. 5. The  $R_{\theta JA}$  is dependent of the PCB heat dissipation and thermal via.

6. The maximum power dissipation ( $P_D$ ) is given by the following formula:

$$\mathsf{P}_\mathsf{D} = \frac{\mathsf{T}_\mathsf{JMAX} - \mathsf{T}_\mathsf{A}}{\mathsf{R}_{\mathsf{\theta}\mathsf{J}\mathsf{A}}}$$

| Symbol              | Parameter                               |                          | Conditions                                       | Min | Тур | Max | Unit |

|---------------------|-----------------------------------------|--------------------------|--------------------------------------------------|-----|-----|-----|------|

| POWER S             | WITCH                                   | -                        |                                                  |     |     |     | -    |

|                     |                                         |                          | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 12  | 20  |      |

|                     |                                         | V <sub>IN</sub> = 5 V    | T <sub>J</sub> = 125°C                           |     |     | 25  |      |

|                     |                                         |                          | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 12  | 20  |      |

|                     |                                         | V <sub>IN</sub> = 3.6 V  | T <sub>J</sub> = 125°C                           |     |     | 25  |      |

|                     |                                         |                          | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 13  | 24  |      |

|                     |                                         | V <sub>IN</sub> = 3.3 V  | T <sub>J</sub> = 125°C                           |     |     | 28  |      |

| D                   | Static drain-source on-state resistance | V <sub>IN</sub> = 2.5 V  | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 13  | 24  | - mΩ |

| R <sub>DS(on)</sub> |                                         |                          | T <sub>J</sub> = 125°C                           |     |     | 28  |      |

|                     |                                         | V <sub>IN</sub> = 1.8 V  | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 13  | 24  |      |

|                     |                                         |                          | T <sub>J</sub> = 125°C                           |     |     | 28  |      |

|                     |                                         | V <sub>IN</sub> = 1.0 V  | $I_{OUT}$ = 200 mA, $T_A$ = 25°C                 |     | 13  | 24  |      |

|                     |                                         |                          | T <sub>J</sub> = 125°C                           |     |     | 28  |      |

|                     |                                         |                          | I <sub>OUT</sub> = 200 mA, T <sub>A</sub> = 25°C |     | 15  | 28  |      |

|                     |                                         | V <sub>IN</sub> = 0.75 V | T <sub>J</sub> = 125°C                           |     |     | 35  |      |

| Rdis                | Output discharge path                   | EN = low                 | NCP451                                           |     | 1.2 | 1.7 | MΩ   |

|                     |                                         |                          | NCP451A                                          |     | 1.0 | 1.7 | kΩ   |

| VIH                 | High-level input voltage                |                          |                                                  | 0.8 |     | 1   |      |

| V <sub>IL</sub>     | Low-level input voltage                 |                          |                                                  |     |     | 0.4 | V    |

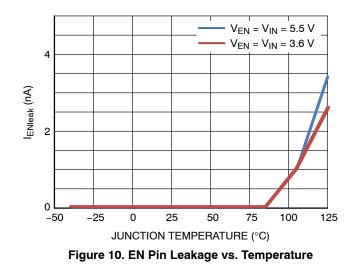

| I <sub>EN</sub>     | EN pin leakage current                  | V <sub>IN</sub> = 3.6 V  |                                                  |     |     | 0.1 | μA   |

**ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-40^{\circ}$ C to  $+85^{\circ}$ C for  $V_{IN}$  between 0.75 V to 5.0 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}$ C and  $V_{IN} = 3.6$  V (Unless otherwise noted).

#### QUIESCENT CURRENT

| Istd | Standby current   | V <sub>IN</sub> = 4.2 V                                                                                                                              | EN = low, No load           | 0.9 | 2  | μA |

|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|----|----|

| lq   | Quiescent current | $\begin{array}{l} V_{IN} = 3.6 \ V \\ V_{IN} = 2.5 \ V \\ V_{IN} = 1.8 \ V \\ V_{IN} = 1.2 \ V \\ V_{IN} = 1.0 \ V \\ V_{IN} = 0.75 \ V \end{array}$ | EN = high, No load (Note 7) | 8   | 15 | μΑ |

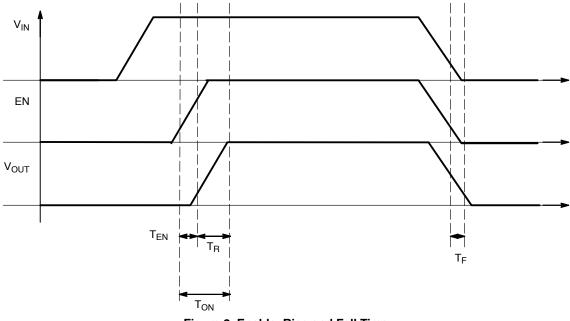

### TIMINGS

| T <sub>EN</sub> | Enable time                                |                         | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                      | 600  |    |

|-----------------|--------------------------------------------|-------------------------|-----------------------------------------------------|------|----|

| Τ <sub>R</sub>  | Output rise time                           | V <sub>IN</sub> = 3.6 V | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                      | 800  |    |

| T <sub>ON</sub> | ON time (T <sub>EN +</sub> T <sub>R)</sub> | (Note 8)                | $R_L$ = 25 Ω, $C_{OUT}$ = 1 μF                      | 1400 | μs |

| Τ <sub>F</sub>  | Output fall time                           |                         | R <sub>L</sub> = 25 Ω, C <sub>OUT</sub> = 1 $\mu$ F | 55   |    |

#### TIMINGS

| T <sub>EN</sub> | Enable time                                |                         | R <sub>L</sub> = 10 Ω, C <sub>OUT</sub> = 0.1 μF | 540  |    |

|-----------------|--------------------------------------------|-------------------------|--------------------------------------------------|------|----|

| Τ <sub>R</sub>  | Output rise time                           | V <sub>IN</sub> = 3.6 V | $R_L$ = 10 $\Omega$ , $C_{OUT}$ = 0.1 $\mu$ F    | 670  |    |

| T <sub>ON</sub> | ON time (T <sub>EN +</sub> T <sub>R)</sub> | (Note 8)                | R <sub>L</sub> = 10 Ω, C <sub>OUT</sub> = 0.1 μF | 1210 | μs |

| Τ <sub>F</sub>  | Output fall time                           |                         | $R_L$ = 10 Ω, $C_{OUT}$ = 0.1 μF                 | 2.5  |    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 7. Production tested at  $V_{IN} = 3.6 V$ . 8. Parameters are guaranteed for  $C_{LOAD}$  and  $R_{LOAD}$  connected to the OUT pin with respect to the ground

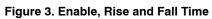

### **ELECTRICAL CURVES**

### ELECTRICAL CURVES

#### FUNCTIONAL DESCRIPTION

#### Overview

The NCP451 is a high side N channel MOSFET power distribution switch designed to isolate ICs connected on the battery in order to save energy. The part can be turned on, with a wide range of battery from 0.75 V to 5.5 V.

#### **Enable Input**

Enable pin is an active high. The path is opened when EN pin is tied low (disable), forcing N-MOSFET switch off.

The IN/OUT path is activated with a minimum of Vin of 0.75 V and EN forced to high level.

#### Auto Discharge

N-MOSFET is placed between the output pin and GND, in order to discharge the application capacitor connected on OUT pin.

#### **Power Dissipation**

Main contributor in term of junction temperature is the power dissipation of the power MOSFET. Assuming this, the power dissipation and the junction temperature in normal mode can be calculated with the following equations:

|                     | $P_{D} = R_{DS(on)} \times \left(I_{OUT}\right)^2$ |

|---------------------|----------------------------------------------------|

| P <sub>D</sub>      | = Power dissipation (W)                            |

| R <sub>DS(on)</sub> | = Power MOSFET on resistance ( $\Omega$ )          |

| I <sub>OUT</sub>    | = Output current (A)                               |

|                     | $T_{J} = P_{D} \times R_{\thetaJA} + T_{A}$        |

| T <sub>J</sub>      | = Junction temperature (°C)                        |

| $R_{\theta JA}$     | = Package thermal resistance (°C/W)                |

| T <sub>A</sub>      | = Ambient temperature (°C)                         |

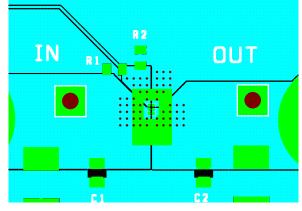

#### **PCB Recommendations**

The NCP451 integrates an up to 3 A rated NMOS FET, and the PCB design rules must be respected to properly evacuate the heat out of the silicon. By increasing PCB area, especially around IN and OUT pins, the  $R_{\theta JA}$  of the package can be decreased, allowing higher power dissipation.

Routing example: 2 oz, 4 layers with vias across 2 internal inners.

The auto-discharge is activated when EN pin is set to low level (disable state).

The discharge path (Pull down NMOS) stays activated as long as EN pin is set at low level and  $V_{IN} > 0.75$  V.

In order to limit the current across the internal discharge N–MOSFET, the typical value is set at R<sub>DIS</sub>.

#### C<sub>IN</sub> and C<sub>OUT</sub> Capacitors

IN and OUT, 1  $\mu$ F, at least, capacitors must be placed as close as possible the part to for stability improvement.

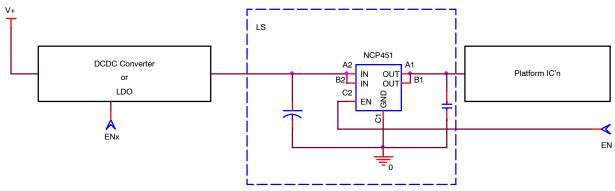

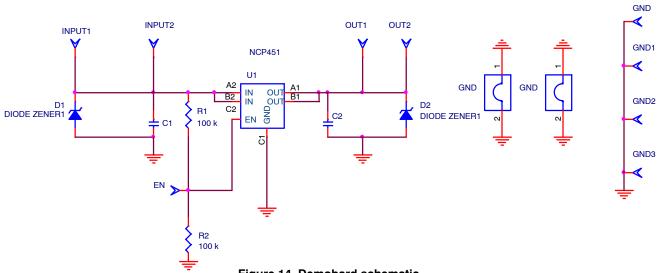

#### **APPLICATION INFORMATION**

Figure 11.

Example of application definition.

$$T_J - T_A = R_{\theta JA} \times R_{DS(on)} \times I^2$$

T<sub>J</sub>: junction temperature.

T<sub>A</sub>: ambient temperature.

Rtheta= Thermal resistance between IC and air, through PCB.

R<sub>DS(on)</sub>: intrinsic resistance of the IC MOSFET. I: load DC current.

Taking into account of Rtheta obtain with:

1 oz, 2 layers: 100°C/W.

At 3 A, 25°C ambient temperature,  $R_{DS(on)}$  20 m $\Omega$  @  $V_{IN}$  5 V, the junction temperature will be:

$$\mathrm{T_J}-\mathrm{T_A}=\mathrm{Rtheta}\times\mathrm{P_D}=\mathrm{25}+\left(\mathrm{0.02}\times\mathrm{3^3}\right)\times\mathrm{100}=\mathrm{43^\circ}\mathrm{C}$$

Taking into account of Rtheta obtain with:

2 oz, 4 layers: 60°C/W.

At 3 A, 65°C ambient temperature,  $R_{DS(on)}$  24 m $\Omega$  @  $V_{IN}$  5 V, the junction temperature will be:

$\textbf{T}_{J} = \textbf{T}_{A} + \textbf{R} \text{theta} \times \textbf{P}_{D} = \textbf{65} + \left(\textbf{0.024} \times \textbf{3}^{2}\right) \times \textbf{60} = \textbf{78}^{\circ}\textbf{C}$

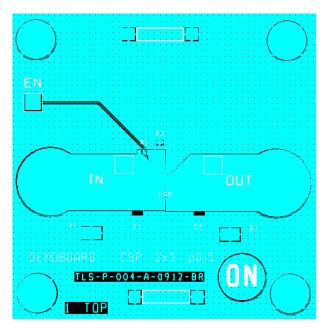

Figure 12. Demoboard PCB Top View

Figure 13. Demoboard PCB Top View

Figure 14. Demobard schematic

### **BILL OF MATERIAL**

| Quantity | Reference Scheme  | Part Description        | Part Number             | Manufacturer |

|----------|-------------------|-------------------------|-------------------------|--------------|

| 2        | IN, OUT           | Socket, 4mm, metal, PK5 | B010                    | HIRSCHMANN   |

| 3        | IN_2, OUT_2, , EN | HEADER200               | 2.54 mm, 77313-101-06LF | FC           |

| 3        | C1, C2            | 1uF                     | GRM155R70J105KA12#      | Murata       |

| 1        | D1, D2            | TVS (not mounted)       | ESD9x                   | onsemi       |

| 2        | GND2,GND          | GND JUMPER              | D3082F05                | Harvin       |

| 2        | R2, R3            | Resistor 100k 0603      | MC 0.063 0603 1% 100K   | MULTICOMP    |

| 1        | U1                | Load switch             | NCP451                  | onsemi       |

#### **ORDERING INFORMATION**

| Device        | Marking | Option                                 | Package                  | Shipping <sup>†</sup> |

|---------------|---------|----------------------------------------|--------------------------|-----------------------|

| NCP451FCT2G   | 451     | Auto Discharge<br>1.2 ΜΩ               | Case 499BR<br>(Pb-Free)  | 3000 / Tape & Reel    |

| NCP451AFCT2G  | 51A     | Auto Discharge<br>1.0 kΩ               | Case 567KB*<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP451AFCCT2G | 51AC    | Auto Discharge<br>1.0 kΩ with ChipCoat | Case 567KB*<br>(Pb-Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*UBM = 205 μm (±8 μm)

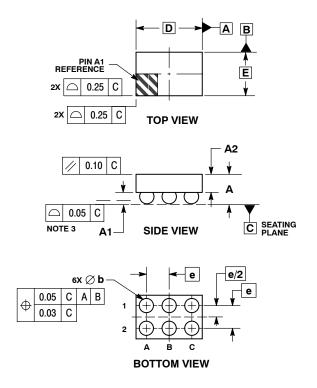

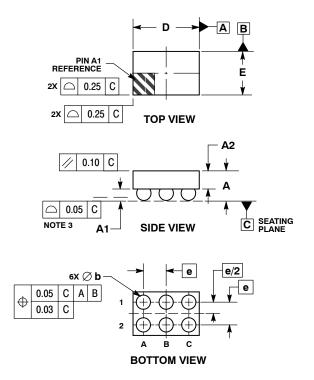

SCALE 4:1

#### WLCSP6, 1.40x0.90 CASE 499BR **ISSUE A**

#### DATE 05 DEC 2012

| ( | CROWNS OF SOLDER E |          |             |  |  |  |

|---|--------------------|----------|-------------|--|--|--|

|   |                    | MILLIN   | MILLIMETERS |  |  |  |

|   | DIM                | MIN MAX  |             |  |  |  |

|   | Α                  |          | 0.50        |  |  |  |

|   | A1                 | 0.17     | 0.23        |  |  |  |

|   | A2                 | 0.25     | REF         |  |  |  |

|   | b                  | 0.21     | 0.25        |  |  |  |

|   | D                  | 1.40 BSC |             |  |  |  |

|   | Е                  | 0.90 BSC |             |  |  |  |

|   | е                  | 0.50     | BSC         |  |  |  |

#### GENERIC **MARKING DIAGRAM\***

= Assembly Location А

- Υ = Year

- WW = Work Week .

- = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

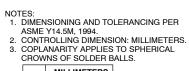

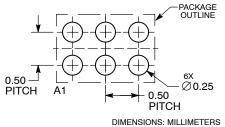

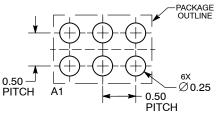

#### RECOMMENDED SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

SCALE 4:1

#### WLCSP6, 1.40x0.90 CASE 567KB **ISSUE A**

#### DATE 22 JUL 2015

NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

| CROWNS OF SOLDER BALLS. |             |             |       |  |  |  |

|-------------------------|-------------|-------------|-------|--|--|--|

|                         | МІ          | MILLIMETERS |       |  |  |  |

| DIM                     | MIN NOM MAX |             |       |  |  |  |

| Α                       |             |             | 0.510 |  |  |  |

| A1                      | 0.142       |             | 0.172 |  |  |  |

| A2                      |             | 0.320       | 0.338 |  |  |  |

| b                       | 0.195       |             | 0.235 |  |  |  |

| D                       |             | 1.400       | 1.440 |  |  |  |

| Е                       |             | 0.900       | 0.940 |  |  |  |

| е                       | 0.50 BSC    |             |       |  |  |  |

### GENERIC **MARKING DIAGRAM\***

= Assembly Location А

Υ = Year

WW = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

#### RECOMMENDED **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.