#### GENERAL DESCRIPTION

The SGM41600 is an efficient 6A switched-capacitor battery charging device with I<sup>2</sup>C control that can operate either in charge-pump voltage divider mode or in bypass mode. It can charge single-cell Li-lon or Li-polymer battery in a wide 3.3V to 11.5V input voltage range (VBUS) from smart wall adapters or power banks. The switched-capacitor architecture is optimized for 50% duty cycle to cut the input current to one-half of the battery current and reduce the wiring drops, losses and temperature rise in the application.

A two-phase switched-capacitor topology is used to reduce the required input capacitors, improve efficiency and minimize the output ripple. Necessary protection features for safe charging performance including input over-voltage protection by external OVPFET ( $Q_{OVP}$ ) and input reverse blocking (using an internal NFET) are provided.

A fast analog-to-digital converter (ADC) with 12-bit effective resolution is also included to measure die temperature, bus voltage, bus current, battery voltage and battery current (5 channels) for battery management of the charge process.

The SGM41600 is available in a Green WLCSP- 2.6×2.6-36B package and can operate in the -40°C to +85°C ambient temperature range.

### **FEATURES**

- Efficiency Optimized Switched-Capacitor Architecture

- Up to 6A Output Current

- 3.3V to 11.5V Input Voltage Range

- 200kHz to 1.5MHz Switching Frequency Setting

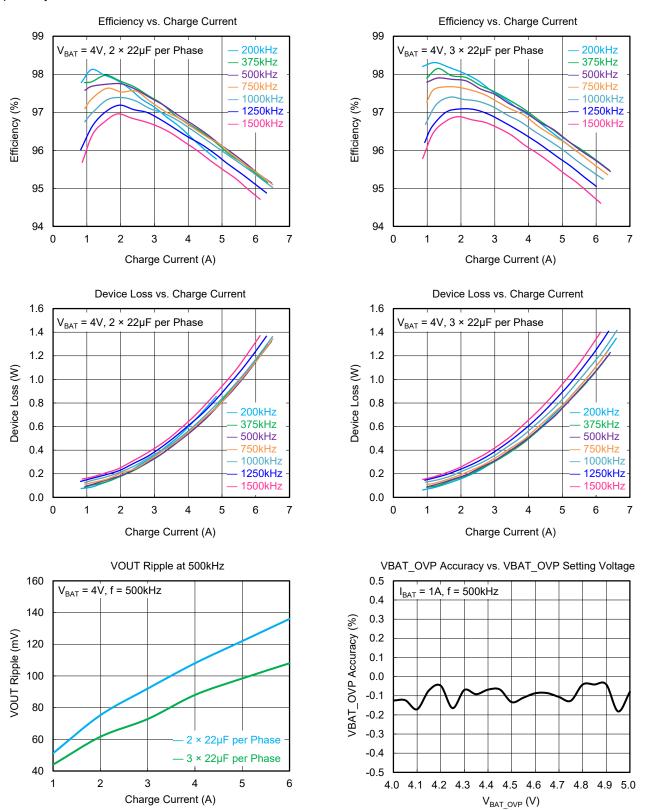

- Up to 97% Voltage Divider Mode Efficiency (when V<sub>BAT</sub> = 4V, I<sub>BAT</sub> = 3A)

- Comprehensive Integrated Protection Features

- External OVP Control and Regulation

- Input Over-Voltage Protection (BUS OVP)

- Input Short-Circuit Protection (BUS SC)

- Input Over-Current Protection (IBUS OCP)

- Input Under-Current Protection (IBUS UCP)

- Battery Over-Voltage Protection (BAT OVP)

- Output Short-Circuit Protection (VOUT SC)

- Battery Over-Current Protection (IBAT OCP)

- CFLY Short-Circuit Protection (CFLY SC)

- Converter Over-Current Protection (CONV OCP)

- Die Over-Temperature Protection (TDIE\_OTP)

- 5-Channel 12-Bit (Effective) ADC Converter

- VBUS, IBUS, VBAT, IBAT, TDIE Monitoring

### **APPLICATIONS**

Smart Phone, Tablet PC

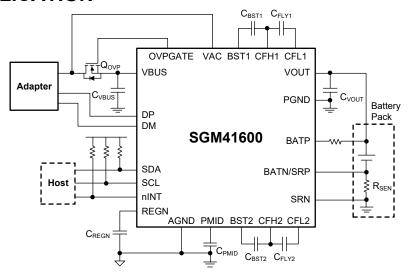

### TYPICAL APPLICATION

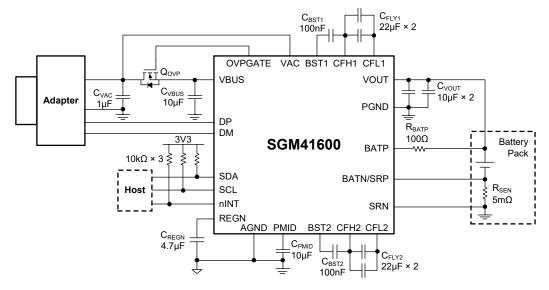

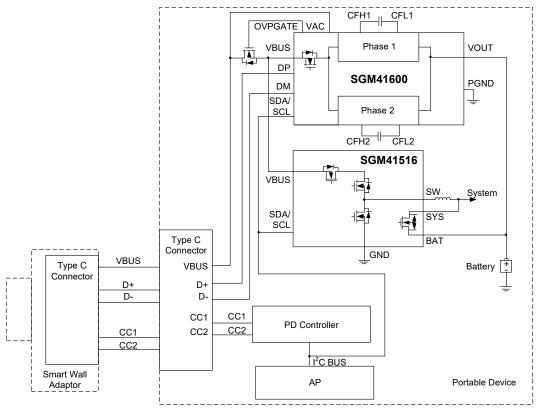

Figure 1. Typical Application Circuit

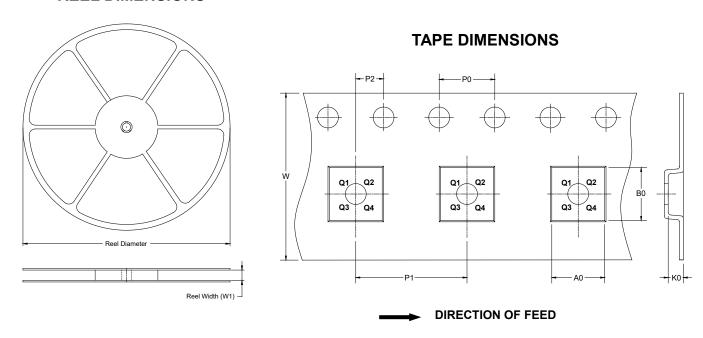

### PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING             | PACKING<br>OPTION   |

|---------|------------------------|-----------------------------------|--------------------|--------------------------------|---------------------|

| SGM4160 | 0 WLCSP-2.6×2.6-36B    | -40°C to +85°C                    | SGM41600YG/TR      | SGM<br>41600<br>XXXXX<br>XX#XX | Tape and Reel, 5000 |

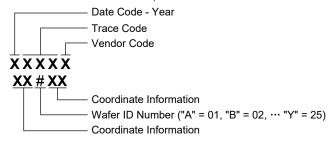

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| 7.2002012 iii. 0.11110111 10.111110  |                  |

|--------------------------------------|------------------|

| VAC (Converter Not Switching)        | 0.3V to 30V      |

| OVPGATE                              | 0.3V to 30V      |

| OVPGATE to VBUS                      | 0.3V to 6V       |

| VBUS, PMID (Converter Not Switching) | 0.3V to 22V      |

| BST1, BST20.3V t                     | to (PMID + 5.5V) |

| VOUT                                 | 0.3V to 6V       |

| CFH1, CFH2 to VOUT                   | 0.3V to 6V       |

| CFL1, CFL2                           | 0.3V to 6V       |

| DP, DM, REGN, BATP, SDA, SDL, nINT   | 0.3V to 6V       |

| BATN/SRP, SRN                        | 0.3V to 1.8V     |

| SRP to SRN                           | 0.5V to 0.5V     |

| Package Thermal Resistance           |                  |

| WLCSP-2.6×2.6-36B, θ <sub>JA</sub>   | 58°C/W           |

| Junction Temperature                 | +150°C           |

| Storage Temperature Range            | -65°C to +150°C  |

| Lead Temperature (Soldering, 10s)    | +260°C           |

| ESD Susceptibility                   |                  |

| HBM                                  |                  |

| CDM                                  | 1000V            |

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### RECOMMENDED OPERATING CONDITIONS

| VAC                                      | 3.3V to 18V    |

|------------------------------------------|----------------|

| OVPGATE                                  | 8V to 23V      |

| VBUS (Bypass Mode)                       | 3.3V to 5.5V   |

| VBUS (Voltage Divider Mode)              | 5.5V to 11.5V  |

| VOUT, BATP                               | 3V to 5V       |

| I <sub>VOUT</sub> (Bypass Mode)          | 0A to 4A       |

| I <sub>VOUT</sub> (Voltage Divider Mode) | 0A to 6A       |

| (CFH1 - VOUT), CFL1                      | 0V to 5.5V     |

| (CFH2 - VOUT), CFL2                      | 0V to 5.5V     |

| BATN/SRP, SRN                            | 0V to 1.5V     |

| (SRP - SRN)                              | 0.05V to 0.05V |

| SDA, SCL, nINT                           | 0V to 5V       |

| Junction Temperature Range               | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

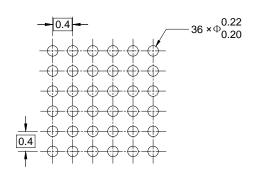

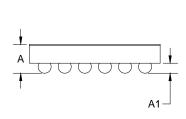

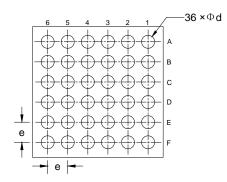

# **PIN CONFIGURATION**

WLCSP-2.6×2.6-36B

# I<sup>2</sup>C Controlled Single-Cell 6A Switched-Capacitor Fast Charger with Bypass Mode and ADC

# **PIN DESCRIPTION**

| PIN            | NAME     | TYPE (1) | FUNCTION                                                                                                                                                                           |

|----------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1             | VAC      | AI       | Adapter DC Voltage Sense Input Pin. Connect it to the drain of the external OVPFET (Q <sub>OVP</sub> ).                                                                            |

| A2, A3, A4, A5 | VBUS     | Р        | Device Power Input Pins. Connect a $10\mu F$ or larger ceramic capacitor between VBUS and PGND pins as close to the device as possible.                                            |

| A6             | OVPGATE  | AO       | External N-FET Gate Control Pin. Connect to the gate of the external OVPFET (Q <sub>OVP</sub> ).                                                                                   |

| B1             | BST1     | Р        | Phase 1 Bootstrap Pin. It is the BST pin to supply $Q_{CH1}$ gate driver. Use a $0.1\mu F$ or larger MLCC capacitor from this pin to CFH1 pin.                                     |

| B2, B5         | PMID     | Р        | Power Stage Supply Input Pins. Bypass them with at least 10µF ceramic capacitor to PGND.                                                                                           |

| В3             | DP       | AIO      | USB Communication Interface Positive Line. Connect to the USB D+ data line.                                                                                                        |

| B4             | DM       | AIO      | USB Communication Interface Negative Line. Connect to the USB D- data line.                                                                                                        |

| В6             | BST2     | Р        | Phase 2 Bootstrap Pin. It is the BST pin to supply Q <sub>CH2</sub> gate driver. Use a 0.1µF or larger MLCC capacitor from this pin to CFH2 pin.                                   |

| C1, C2         | CFH1     | Р        | Phase 1 Flying Capacitor Positive Pins. Connect two 22µF or larger parallel capacitors between CFH1 and CFL1 pins as close as possible to the device.                              |

| C3             | SDA      | DIO      | I <sup>2</sup> C Interface Data Line.                                                                                                                                              |

| C4             | SCL      | DI       | I <sup>2</sup> C Interface Clock Input Line.                                                                                                                                       |

| C5, C6         | CFH2     | Р        | Phase 2 Flying Capacitor Positive Pins. Connect two 22µF or larger parallel capacitors between CFH2 and CFL2 pins as close as possible to the device.                              |

| D1, D2, D5, D6 | VOUT     | Р        | Output Pins. Connect to the battery pack positive terminal. Two 10µF capacitors between VOUT and PGND pins are recommended.                                                        |

| D3             | BATN/SRP | Al       | Battery Voltage Sensing Negative Input or Battery Current Sensing Positive Input.                                                                                                  |

| D4             | SRN      | Al       | Battery Current Sensing Negative Input. Place a $5m\Omega$ ( $R_{SEN}$ ) shunt resistor between SRN and BATN/SRP pins.                                                             |

| E1, E2         | CFL1     | Р        | Phase 1 Flying Capacitor Negative Pins. Connect two 22µF or larger parallel capacitors between CFH1 and CFL1 pins as close as possible to the device.                              |

| E3             | BATP     | Al       | Battery Voltage Sensing Positive Input. Connect a $100\Omega$ resistor between BATP and positive terminal of the battery pack.                                                     |

| E4             | nINT     | DO       | Open-Drain Interrupt Output Pin. Connect a pull-up 10kΩ to the logic high rail. It is normally high but generates a low 256μs pulse when a charge fault occurs to inform the host. |

| E5, E6         | CFL2     | Р        | Phase 2 Flying Capacitor Negative Pins. Connect two 22µF or larger parallel capacitors between CFH2 and CFL2 pins as close as possible to the device.                              |

| F1, F2, F5, F6 | PGND     | Р        | Power Ground Pin.                                                                                                                                                                  |

| F3             | AGND     | Р        | Analog Ground Pin (reference for low current signals).                                                                                                                             |

| F4             | REGN     | AO       | Internal 3.3V LDO Output. Connect a 4.7µF MLCC capacitor between this pin and AGND.                                                                                                |

#### NOTE

1. P = power, AI = analog input, AO = analog output, AIO = analog input/output, DI = digital input, DO = digital output, DIO = digital input/output.

# **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ typical values are at } T_J = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                                    | SYMBOL                       | CONDITIONS                                                                                                                                                                                                  | MIN                             | TYP      | MAX                            | UNITS    |

|--------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|--------------------------------|----------|

| Supply Currents                                              | •                            |                                                                                                                                                                                                             |                                 |          |                                |          |

| VAC Input Quiescent Current<br>(No VBUS or BAT sources)      | I <sub>Q_VAC</sub>           | ADC disabled, charge disabled, $Q_{OVP}$ used, VAC OVP activated, $V_{VAC}$ = 12V, $V_{VBUS}$ = 0V, $V_{VOUT}$ = 0V                                                                                         |                                 | 200      | 280                            | μΑ       |

| VBUS Power Input Quiescent<br>Current (1)                    | I <sub>Q_VBUS</sub>          | ADC disabled, charge disabled, Q <sub>OVP</sub> used, V <sub>VBUS</sub> = 8V ADC enabled, charge enabled, Q <sub>OVP</sub> used,                                                                            |                                 | 50<br>10 | 70                             | μA<br>mA |

|                                                              |                              | V <sub>VBUS</sub> = 8V > 2 × V <sub>VOUT</sub> , f <sub>SW</sub> = 500kHz ADC disabled, charge disabled,                                                                                                    |                                 | 10       | 30                             | μA       |

| Battery-Only Quiescent Current                               | I <sub>Q_VOUT</sub>          | VBUS not present, V <sub>VAC</sub> = 0V, V <sub>VOUT</sub> = 4.5V  ADC enabled, charge disabled, (after 1-shot ADC conversion complete), VBUS not present,  V <sub>VAC</sub> = 0V, V <sub>VOUT</sub> = 4.5V |                                 | 10       | 30                             | μА       |

| VBUS Present Rising Threshold                                | V <sub>BUS_PRESENT_R</sub>   | V <sub>VBUS</sub> rising                                                                                                                                                                                    |                                 | 3        | 3.3                            | V        |

| VBUS Present Hysteresis                                      | V <sub>BUS_PRESENT_HYS</sub> |                                                                                                                                                                                                             |                                 | 240      |                                | mV       |

| External OVP Control                                         |                              |                                                                                                                                                                                                             |                                 |          |                                |          |

| VAC Present Rising Threshold                                 | V <sub>VAC_PRESENT_R</sub>   | V <sub>VAC</sub> rising                                                                                                                                                                                     |                                 | 3        | 3.35                           | V        |

| VAC Present Hysteresis                                       | V <sub>VAC_PRESENT_HYS</sub> |                                                                                                                                                                                                             |                                 | 160      |                                | mV       |

| VAC Present Rising Threshold<br>Deglitch Time <sup>(1)</sup> | t <sub>VAC_IN_DEG</sub>      | $V_{\text{BAT}}$ = 4V, deglitch between $V_{\text{VAC}}$ rising above $V_{\text{VAC PRESENT R}}$ and starting external OVPFET turn-on                                                                       |                                 | 20       |                                | ms       |

| VAC OVP Rising Threshold                                     | $V_{VAC\_OVP}$               | l <sup>2</sup> C programmable, 1V per step, 12V by default                                                                                                                                                  | 4                               |          | 19                             | V        |

| VAC OVP Threshold Accuracy                                   | V <sub>VAC_OVP_ACC</sub>     | V <sub>VAC_OVP</sub> = 5V or 12V                                                                                                                                                                            | -2.7                            |          | 3.7                            | %        |

| VAC OVP Rising<br>Deglitch Time <sup>(1)</sup>               | t <sub>VAC_OVP_DEG</sub>     | Deglitch between $V_{\text{VAC}}$ rising above $V_{\text{VAC\_OVP}}$ and triggering the protection action                                                                                                   |                                 | 100      |                                | ns       |

| VBUS Pull-Down Resistor                                      | R <sub>PD_VBUS</sub>         | V <sub>VBUS</sub> = 2V                                                                                                                                                                                      |                                 | 1        |                                | kΩ       |

| VAC Pull-Down Resistor                                       | R <sub>PD_VAC</sub>          |                                                                                                                                                                                                             |                                 | 60       | 70                             | Ω        |

| VAC Pull-Down Timeout (1)                                    | t <sub>VAC_PD</sub>          | AC_PDN_EN = 1                                                                                                                                                                                               |                                 | 400      |                                | ms       |

| VBAT Regulation Range                                        | $V_{BAT\_REG}$               | I <sup>2</sup> C programmable, 50mV per step                                                                                                                                                                | V <sub>BAT_OVP</sub> - 200mV    |          | V <sub>BAT_OVP</sub><br>- 50mV |          |

| VBAT Regulation Accuracy                                     | V <sub>BAT_REG_ACC</sub>     | $V_{BAT\_REG} = 4.3V$ , $T_J = +25$ °C                                                                                                                                                                      | -0.4                            |          | 0.4                            | %        |

|                                                              | V BAT_REG_ACC                | $V_{BAT\_REG} = 4.3V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                                                                         | -0.8                            |          | 0.8                            | 70       |

| VBAT Regulation Entry<br>Deglitch Time <sup>(1)</sup>        | t <sub>VBAT_IN_DEG</sub>     | Deglitch between V <sub>BAT</sub> rising above V <sub>BAT_REG</sub> (entering regulation mode), and flag bit set to 1                                                                                       |                                 | 500      |                                | μs       |

| IBAT Regulation Range                                        | I <sub>BAT_REG</sub>         | I <sup>2</sup> C programmable, 100mA per step                                                                                                                                                               | I <sub>ват_оср</sub><br>- 500mA |          | I <sub>BAT_OCP</sub> - 200mA   |          |

| IBAT Regulation Accuracy                                     | I <sub>BAT_REG_ACC</sub>     | $I_{BAT} = 4A$ , $R_{SEN} = 5m\Omega$ , $T_J = +25^{\circ}C$                                                                                                                                                | -5.5                            |          | 5                              | %        |

| IBAT Regulation Entry<br>Deglitch Time <sup>(1)</sup>        | t <sub>IBAT_IN_DEG</sub>     | Deglitch between I <sub>BAT</sub> rising above I <sub>BAT_REG</sub> (entering regulation mode ) and flag bit set to 1                                                                                       |                                 | 500      |                                | μs       |

| <b>Switched Capacitor Chargers</b>                           |                              |                                                                                                                                                                                                             |                                 |          |                                |          |

| VBUS to VOUT Resistance                                      | R <sub>DROPOUT</sub>         | Bypass mode                                                                                                                                                                                                 |                                 | 30       | 45                             | mΩ       |

| R <sub>DSON</sub> of Reverse Blocking FET                    | R <sub>DS_QRB</sub>          | $V_{VBUS} = 10V$ , $V_{VOUT} = 5V$ , $I_{BAT} = 1A$                                                                                                                                                         |                                 | 10       | 18                             | mΩ       |

| R <sub>DSON</sub> of Q <sub>CH1/2</sub>                      | R <sub>DS_QCH</sub>          | V <sub>VBUS</sub> = 10V, V <sub>VOUT</sub> = 5V, I <sub>BAT</sub> = 1A                                                                                                                                      |                                 | 26       |                                | mΩ       |

| R <sub>DSON</sub> of Q <sub>DH1/2</sub>                      | R <sub>DS_QDH</sub>          | V <sub>VBUS</sub> = 10V, V <sub>VOUT</sub> = 5V, I <sub>BAT</sub> = 1A                                                                                                                                      |                                 | 14       |                                | mΩ       |

| R <sub>DSON</sub> of Q <sub>CL1/2</sub>                      | R <sub>DS_QCL</sub>          | V <sub>VBUS</sub> = 10V, V <sub>VOUT</sub> = 5V, I <sub>BAT</sub> = 1A                                                                                                                                      |                                 | 14       |                                | mΩ       |

| R <sub>DSON</sub> of Q <sub>DL1/2</sub>                      | R <sub>DS_QDL</sub>          | V <sub>VBUS</sub> = 10V, V <sub>VOUT</sub> = 5V, I <sub>BAT</sub> = 1A                                                                                                                                      |                                 | 14       |                                | mΩ       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ typical values are at } T_J = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| DADAMETED                                        |                            | CONDITIONS                                                                                                                 | NAIN! | TVD | MAY   | LINUTO |

|--------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|--------|

| PARAMETER                                        | SYMBOL                     | CONDITIONS                                                                                                                 | MIN   | TYP | MAX   | UNITS  |

| Protection                                       | T                          |                                                                                                                            | 1     |     | 1     | ı      |

| nINT Low Pulse Duration when a Protection Occurs | t <sub>INT</sub>           |                                                                                                                            |       | 256 |       | μs     |

| VBUS OVP Rising Threshold Programming Range      | $V_{BUS\_OVP}$             | I <sup>2</sup> C programmable, 100mV per step, 11.5V by default                                                            | 4     |     | 14    | V      |

| VBUS OVP Threshold Accuracy                      | $V_{BUS\_OVP\_ACC}$        | V <sub>BUS_OVP</sub> = 5V or 11.5V                                                                                         | -3.5  |     | 2     | %      |

| VBUS OVP Rising Deglitch Time (1)                | t <sub>VBUS_OVP_DEG</sub>  | Deglitch between V <sub>VBUS</sub> rising above V <sub>BUS_OVP</sub> and triggering protection action                      |       | 100 |       | ns     |

| IBUS OCP Threshold Programming                   | 1                          | Voltage divider   I <sup>2</sup> C programmable,<br>mode   100mA per step, 3A by default                                   | 0.5   |     | 3.6   | А      |

| Range                                            | I <sub>BUS_OCP</sub>       | Bypass mode l <sup>2</sup> C programmable,<br>100mA per step, 5A by default                                                | 2.5   |     | 5.6   | ^      |

| IBUS OCP Threshold Initial Accuracy              | I <sub>BUS_OCP_ACC</sub>   | $I_{BUS} = 2.5A, T_J = +25^{\circ}C$                                                                                       | -6    |     | 6     | %      |

| IBUS OCP Deglitch Time                           | t <sub>IBUS_OCP_DEG</sub>  | Deglitch between I <sub>BUS</sub> rising above I <sub>BUS_OCP</sub> and triggering protection action                       |       | 50  |       | μs     |

| IDLIQUIOD District Through all                   |                            | Rising, set by REG0x07[6] = 0                                                                                              | 200   | 300 | 400   | 4      |

| IBUS UCP Rising Threshold                        | I <sub>BUS_UCP_R</sub>     | Rising, set by REG0x07[6] = 1                                                                                              | 400   | 500 | 600   | mA     |

| IBUS UCP Rising Deglitch Time                    | t <sub>IBUS_UCPR_DEG</sub> | Deglitch between I <sub>BUS</sub> rising above I <sub>BUS_UCP_R</sub> and triggering protection action                     |       | 10  |       | μs     |

| IDUO HOD E III TI I I I                          |                            | Falling, set by REG0x07[6] = 0                                                                                             |       | 150 | 250   |        |

| IBUS UCP Falling Threshold                       | I <sub>BUS_UCP_F</sub>     | Falling, set by REG0x07[6] = 1                                                                                             | 150   | 250 | 350   | mA     |

| IBUS UCP Falling Deglitch Time                   | t <sub>IBUS_UCPF_DEG</sub> | Deglitch between I <sub>BUS</sub> falling below I <sub>BUS_UCP_F</sub> and triggering protection action                    |       | 10  |       | μs     |

| VBAT OVP Rising Threshold Programming Range      | $V_{BAT\_OVP}$             | I <sup>2</sup> C programmable, 25mV per step,<br>4.35V by default                                                          | 4     |     | 5     | V      |

| VBAT OVP Threshold Accuracy                      | $V_{BAT\_OVP\_ACC}$        | $V_{BAT\_OVP} = 4.35V$                                                                                                     | -0.5  |     | 0.5   | %      |

| VBAT OVP Rising Deglitch Time                    | t                          | Deglitch between V <sub>BAT</sub> rising above V <sub>BAT_OVP</sub> and triggering protection action                       |       | 8   |       | μs     |

| VB/(I OVI Tribing Degition Time                  | t <sub>VBAT_OVP_DEG</sub>  | During VBAT_REG                                                                                                            |       | 500 |       | μs     |

| IBAT OCP Threshold Programming Range             | I <sub>BAT_OCP</sub>       | l <sup>2</sup> C programmable, 100mA per step,<br>7.2A by default                                                          | 2     |     | 7.2   | Α      |

| IBAT OCP Threshold Accuracy                      | I <sub>BAT_OCP_ACC</sub>   | $I_{BAT} = 4A, R_{SEN} = 5m\Omega, T_{J} = +25^{\circ}C$                                                                   | -5.5  |     | 5.5   | %      |

| IBAT OCP Deglitch Time                           | t <sub>IBAT_OCP_DEG</sub>  | Deglitch between I <sub>BAT</sub> rising above I <sub>BAT_OCP</sub> and triggering protection action                       |       | 50  |       | μs     |

| 12/11 COI Degittori Time                         | "IBAT_OCP_DEG              | During IBAT_REG                                                                                                            |       | 500 |       | μs     |

| VDRP OVP Threshold Programming Range             | $V_{DRP}_{OVP}$            | I <sup>2</sup> C programmable, 50mV per step,<br>300mV by default, V <sub>DRP</sub> = V <sub>VAC</sub> - V <sub>VBUS</sub> | 50    |     | 400   | mV     |

| TDIE OTP Rising Threshold                        | T <sub>DIE_OTP</sub>       |                                                                                                                            |       | 150 |       | °C     |

| Watchdog Timeout Programming Range (1)           | t <sub>WDT</sub>           | I <sup>2</sup> C programmable, 0.5s by default                                                                             | 0.5   |     | 80    | s      |

| ADC Specification                                |                            |                                                                                                                            | •     |     |       | •      |

| ADC Resolution                                   | ADC <sub>RES</sub>         |                                                                                                                            |       | 12  |       | bits   |

| ADC Conversion Time (1)                          | t <sub>ADC_CONV</sub>      | Report data for each channel                                                                                               |       | 3   | 3.5   | ms     |

| ADC BUS Voltage Readable in                      | .,                         | Range                                                                                                                      | 0     |     | 16.38 | V      |

| REG0x12 and REG0x13                              | $V_{BUS\_ADC}$             | LSB                                                                                                                        |       | 4   |       | mV     |

| ADC BUS Voltage Accuracy                         | V <sub>BUS_ADC_ACC</sub>   | $V_{VBUS} = 3.3V$ to 11.5V, $T_J = 0^{\circ}C$ to +85°C                                                                    | -2.5  |     | 2     | %      |

| ADC BUS Current Readable in                      | I <sub>BUS ADC</sub>       | Range                                                                                                                      | 0     |     | 8.19  | Α      |

| REG0x14 and REG0x15                              | 203_100                    | LSB                                                                                                                        |       | 2   |       | mA     |

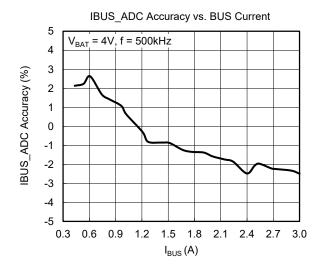

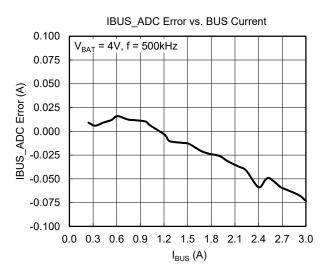

| ADC BUS Current Accuracy                         | I <sub>BUS_ADC_ACC</sub>   | $I_{BUS} = 2A, T_{J} = 0^{\circ}C \text{ to } +85^{\circ}C$                                                                |       | 2   |       | %      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are at } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                | SYMBOL                                | CONDITIONS                                                     | MIN   | TYP  | MAX  | UNITS |

|------------------------------------------|---------------------------------------|----------------------------------------------------------------|-------|------|------|-------|

| ADC BAT Voltage Readable in              | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Range                                                          | 0     |      | 5.5  | V     |

| REG0x16 and REG0x17                      | V <sub>BAT_ADC</sub>                  | LSB                                                            |       | 2    |      | mV    |

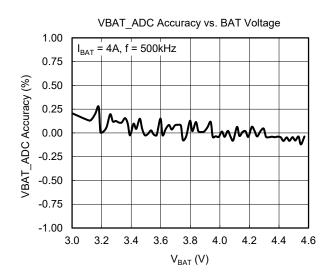

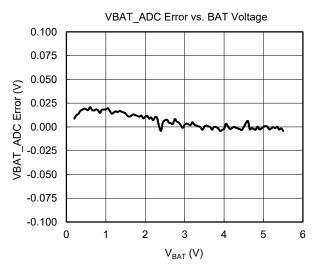

| ADC BAT Voltage Initial Accuracy         | V <sub>BAT_ADC_ACC</sub>              | V <sub>BAT</sub> = 3V to 4.8V, T <sub>J</sub> =+25°C           | -0.85 |      | 0.75 | %     |

| ADC BAT Current Readable in              |                                       | Range                                                          | 0     |      | 8.19 | Α     |

| REG0x18 and REG0x19                      | I <sub>BAT_ADC</sub>                  | LSB                                                            |       | 2    |      | mA    |

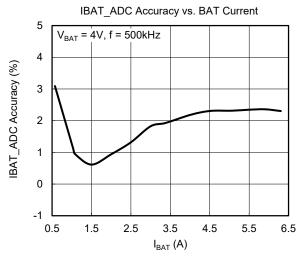

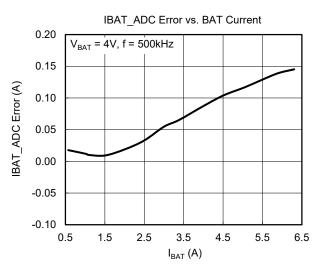

| ADC BAT Current Initial Accuracy         | I <sub>BAT_ADC_ACC</sub>              | $I_{BAT} = 4A$ , $R_{SEN} = 5m\Omega$ , $T_{J} = +25^{\circ}C$ |       |      | 7.5  | %     |

| ADC TDIE Temperature Readable in         | _                                     | Range                                                          | -40   |      | 150  | °C    |

| REG0x1A                                  | T <sub>DIE_ADC</sub>                  | LSB                                                            |       | 1    |      | °C    |

| ADC TDIE Temperature Accuracy            | T <sub>DIE_ADC_ACC</sub>              |                                                                |       | ±4   |      | °C    |

| Logic I/O Threshold (SCL, SDA and n      | NT Pins)                              |                                                                |       |      |      |       |

| High Level Input Voltage                 | V <sub>IH_I2C</sub>                   | SCL and SDA pins                                               | 1.3   |      |      | V     |

| Low Level Input Voltage                  | V <sub>IL_I2C</sub>                   | SCL and SDA pins                                               |       |      | 0.4  | V     |

| Low Level Output Voltage                 | V <sub>OL_I2C</sub>                   | Sink 5mA, SDA and nINT pins                                    |       |      | 0.4  | V     |

| I <sup>2</sup> C Characteristics         |                                       |                                                                |       |      |      |       |

| CCI Clark Francisco                      |                                       | Fast-mode                                                      |       | 400  |      | 1411- |

| SCL Clock Frequency                      | f <sub>CLK</sub>                      | Fast-mode plus                                                 |       | 1000 |      | kHz   |

| DP/DM Detection                          | •                                     |                                                                |       |      |      |       |

| DP Force Detection Voltage               | V <sub>DP_SRC</sub>                   |                                                                | 0.55  | 0.6  | 0.65 | V     |

| DM Pull-Down Detection Threshold         | V <sub>DAT_REF</sub>                  |                                                                |       |      | 0.4  | V     |

| DM Pull-Down Detection Debounce Time (1) |                                       |                                                                |       | 60   |      | ms    |

#### NOTE:

1. Guaranteed by design.

### TYPICAL PERFORMANCE CHARACTERISTICS

Typical performance characteristics are taken with test equipment and the demo board for non-switching and switching tests, respectively.

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Typical performance characteristics are taken with test equipment and the demo board for non-switching and switching tests, respectively.

### TYPICAL APPLICATION CIRCUIT

Figure 2. Typical Application Circuit

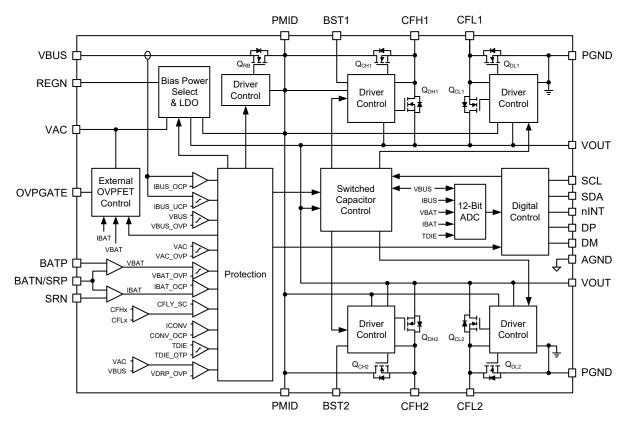

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Functional Block Diagram

#### DETAILED DESCRIPTION

The SGM41600 is an efficient 6A battery charger that operates in voltage divider mode (switched-capacitor charge pump) or in bypass mode. A two-phase switched-capacitor core is integrated in the device to minimize the ripples and improve efficiency in the voltage divider mode. A FET control output for protection, a reverse blocking NFET and all other necessary protection features for safe charging are included. A high speed 12-bit ADC converter is also included to provide bus voltage, bus current, battery voltage, battery current, and die temperature information for the charge management host via I<sup>2</sup>C serial interface.

#### **Charge-Pump Voltage Divider Mode**

The charge-pump voltage divider mode operates with a fixed 50% duty cycle. The basic principle of operation is shown in Figure 4. In period 1, Q1 and Q3 are tuned on and  $V_{PMID}$  charges the  $C_{FLY}$  and the battery (in series) such that:

$$V_{CFLY} = V_{PMID} - V_{BAT}$$

(1)

In period 2, Q2 and Q4 are turned on and  $C_{\text{FLY}}$  appears in parallel with the battery:

$$V_{CFLY} = V_{BAT}$$

(2)

Ignoring the small fluctuation of the capacitor and battery voltages in period 1 and 2 in steady state operation, Equation 1 and 2 can be combined to calculate capacitor voltage:

$$V_{CFLY} = V_{BAT} = V_{PMID}/2$$

(3)

Ignoring small energy loss in each switching period, the input and output cycle-average powers are equal. Therefore,

$$V_{PMID} \times I_{BUS} = V_{BAT} \times I_{BAT}$$

(4)

or

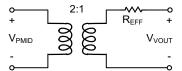

Figure 4. Voltage Divider Charger Operating Principle

Assuming no charge leakage path and considering  $R_{\text{EFF}}$  as the effective input to output resistance (due to the switch on-resistances and  $C_{\text{FLY}}$  losses), the divider can be modeled as shown in Figure 5. Using this model, the output voltage is

half of the input voltage under no load conditions as explained before. The SGM41600 has two phases of such architecture operating at  $f_{SW}$  frequency with 180° phase difference. Each phase provides  $I_{VOUT}/2$  at the VOUT node, so:

$$V_{VOUT} = \frac{1}{2}V_{PMID} - \frac{1}{2}R_{EFF} \times I_{VOUT}$$

(6)

At low switching frequencies the capacitor charge sharing losses are dominant and  $R_{EFF}\approx 1/(4f_{SW}C_{FLY}).$  As frequency increases,  $R_{EFF}$  finally approaches ( $R_{DS\_QCH}$  +  $R_{DS\_QDL}$  +  $R_{DS\_QDL}$ )/2.

Figure 5. Model of Voltage Divider

The two-phase interleaved operation ensures a smooth input current and simplifies the noise filtering. The VOUT ripple can be estimated by first order approximation of C<sub>FLY</sub> voltage drop due to the discharge in the half period, plus the discharge drop during the short dead time (15ns, TYP).

Selecting high quality  $C_{\text{FLY}}$  capacitors and proper switching frequency are the key factors for a well performing capacitor voltage divider. Switching frequency selection is a trade-off between efficiency and capacitor size. Lower frequency increases efficiency by reducing switching losses but requires larger capacitance to maintain low output ripple and low output impedance ( $R_{\text{EFF}}$ ). An optimum switching frequency can be found for any selected  $C_{\text{FLY}}$  capacitor to minimize losses.

#### Bypass Mode

The SGM41600 is designed to operate in bypass mode when  $V_{BUS}$  is close to the  $V_{VOUT}$ . When such valid voltage is present on VBUS, the device enters bypass mode and all switches between VBUS and VOUT are fully turned on while the other switches are kept off. When  $V_{BUS}$  is near  $V_{VOUT}$ , the bypass mode offers the best efficiency and the device is capable of sourcing up to 5.6A (Maximum 4A continuous current is recommended in this mode).

The output voltage is close to the  $V_{\text{BUS}}$  minus a voltage drop caused by the on-resistances of the RBFET plus the two high-side switches of the two phases in parallel. So the REFF in bypass mode is:

$$R_{\text{EFF}}(\text{Bypass mode}) \approx \left(R_{\text{DS\_QCH1}} + R_{\text{DS\_QDH1}}\right) || \left(R_{\text{DS\_QCH2}} + R_{\text{DS\_QDH2}}\right) \ \ \, (7)$$

where  $R_{DS}$  QXX is the on-resistance of the switch xx.

#### **Charge System**

The SGM41600 is a slave charger device and needs a host. The host must set up all protection functions and disable the main charger before enabling the SGM41600. The host must monitor the nINT interrupts especially during high current charging. It must also communicate with the wall adapter to control the charge current.

Figure 6 shows the block diagram of a charge system using the SGM41600 along with a PD controller and other devices. In this system, the SGM41600 can be used to detect the adapter by USB BC1.2. It allows each of the D+/D- lines to be controlled independently to output one of the preset voltage levels (0V, 0.6V, 1.2V, 2.0V, 2.7V, 3.3V, and Hi-Z). Each line can be set to one of these presets via I<sup>2</sup>C in REG0x36. This allows the implementation of a handshaking protocol between the charger and an adapter with an interface that allows adjusting the voltage. Since the adapter voltage is controllable, the operating point of the charger can be fine-tuned to ensure high efficiency during charging. When the smart wall adapter is detected, the AP unit controls the switching charger (SGM41516) that powers the load system and the switched capacitor charger (SGM41600) that provides high current charging. The communication between those devices is via I<sup>2</sup>C serial interface.

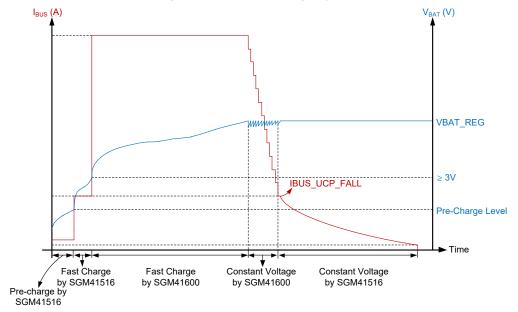

A typical charge profile for a high-capacity battery using switching charger and switched capacitor charger together is shown in Figure 7. During the trickle charge and pre-charge, the charging is controlled by the switching charger. Once the battery voltage reaches 3V, the adapter can negotiate for a higher bus voltage and enable the SGM41600 for charging

(bypass or voltage divider mode). Once the battery voltage reaches the  $V_{BAT\_REG}$  point, the SGM41600 provides feedback to the adapter to reduce the current. This will eventually reduce and ramp down the bus current below  $I_{BUS\_UCP\_F}$ .

#### **Startup Sequence**

The SGM41600 is powered from the greater of VAC or VOUT (VAC is used as sense input for adapter voltage as well). The internal watchdog timer is enabled by default and if no I<sup>2</sup>C read or write occurs before its expiry, the ADC\_EN and CHG\_MODE bits are reset to their default values and after an initial 8ms power-up time, an INT pulse is triggered to show watchdog timeout. The host should not attempt to read or write before this initial nINT signal.

The device does not start charging after powered up, because by default the charger is disabled. The ADC can be enabled and the host can read the system parameters before enabling charge. The charge can be enabled only if  $V_{VBUS} > V_{BUS\ PRESENT\ R}$  and  $V_{BATP} > 2.8V$ .

# **Device Power-Up from Battery without Input Source**

To reduce the quiescent current and maximize the battery run time when it is the only available source, the REGN LDO and most of the sensing circuits are turned off, except AC\_PRESENT, BUS\_INSERT and BAT\_INSERT functions. When the BUS\_PDN\_EN bit is set, the external OVPFET is turned off, and VBUS pull-down  $R_{\text{PD}\_\text{VBUS}}$  is activated to help discharging VBUS after a hot-plug event. This will keep the device in low quiescent current mode even after an input source is plugged.

Figure 6. Simplified Charge System

Figure 7. SGM41600 System Charging Profile

#### **Device Power-Up from Input Source**

When an input source is plugged-in and the  $V_{VBUS} > V_{BUS\_PRESENT\_R}$  condition is valid, the host must initialize all protections to the desired thresholds before enabling charge. The protection thresholds that need to be set are AC\_OVP, VBUS\_LO, VBUS\_HI, BUS\_OVP, IBUS\_OCP, IBUS\_UCP, BAT\_OVP, IBAT\_OCP, VBAT\_REG, IBAT\_REG, and VDRP\_OVP. If one of the protection trigger conditions is met, the charger stops switching. It will also turn off the external OVPFET when AC\_OVP or BUS\_SC event occurs.

After setting protections, the VBUS voltage is checked to be between 2 ×  $V_{BUS\_LO}$  ×  $V_{VOUT}$  and 2 ×  $V_{BUS\_HI}$  ×  $V_{VOUT}$  to allow voltage divider mode operation, or between  $V_{BUS\_LO}$  ×  $V_{VOUT}$  and  $V_{BUS\_HI}$  ×  $V_{VOUT}$  for bypass mode operation. Charging is enabled and current flows into the battery when the host sets bypass or voltage divider mode by writing 001 or 010 in the CHG\_MODE[2:0] bits respectively. Then raising the VBUS voltage will increase the battery charge current. When the converter is on, any command to change the charge mode is ignored. To do so, the charging must be disabled first, and then the charge mode can be changed by  $I^2C$  serial interface.

#### **REGN Management**

The SGM41600 internal digital core is powered by the REGN LDO. This LDO is enabled and powered by PMID. A  $4.7\mu F$  or lager capacitor is required on the REGN pin.

#### **ADC**

The SGM41600 integrates a fast 5-channel, 12-bit ADC converter to monitor input/output currents and voltages and the temperature of the device. The ADC is controlled by the

ADC\_CTRL register. Setting the ADC\_EN bit to 1 enables the ADC. This bit can be used to turn off the ADC and save power when it is not needed. The ADC\_RATE bit allows choosing continuous conversion or 1-shot conversion mode. The ADC operates independent of the faults, unless the host sets the ADC EN bit to 0.

The ADC can operate if  $V_{VBUS} > V_{BUS\_PRESENT\_R}$  or  $V_{BATP} > 2.8V$  condition is valid. Otherwise the ADC conversion is postponed until one of them is satisfied. The ADC readings are valid only for DC values and not for transients.

By default, all ADC channels are converted in continuous conversion mode except the channels disabled by the ADC\_CTRL register. If the 1-shot conversion mode is selected, the ADC\_DONE\_FLAG bit is set to 1 when all channels are converted, then the ADC\_EN bit is reset to 0. In the continuous conversion mode, the ADC\_DONE\_FLAG bit is set to 0.

#### nINT Pin, Flag and Mask Bits

The nINT pin is an open-drain output and must be pulled up to a logic high rail. It is pulled low with a duration of  $t_{\text{INT}}$  to notify the host when it is triggered by an event. See the register map for all event flag and control bits.

When an event occurs, a nINT signal is sent to the host and the corresponding flag bit is set to 1. The flag bit can be reset by read only after the fault is cleared. The nINT signal is not re-sent if an event is still present after the flag bit is read, unless another kind of event occurs. If an event mask bit is set, that event will not send nINT signal, but the flag bit is still updated independent of the mask bit.

#### **Fault Event and Protection Status**

Table 1 shows the protection features and corresponding conditions of the device.

#### VAC Over-Voltage Protection (AC\_OVP)

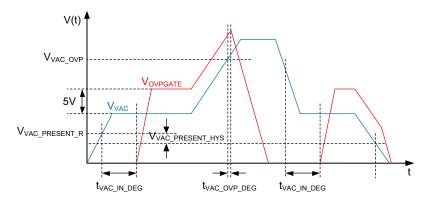

The SGM41600 monitors the adapter voltage on the VAC pin to control the external OVPFET using OVPGATE output. The VAC over-voltage protection circuit is powered by VAC and is enabled if  $V_{VAC}$  rises above  $V_{VAC\_PRESENT\_R}$ . If  $V_{VAC}$  is above  $V_{VAC\_PRESENT\_R}$  for at least  $t_{VAC\_IN\_DEG}$  time, a 5V gate voltage

is sent to the OVPGATE output to turn on the external OVPFET. If the  $V_{VAC}$  reaches the  $V_{VAC\_OVP}$  threshold for  $t_{VAC\_OVP\_DEG}$  deglitch time, the gate voltage starts to drop. Figure 8 shows the AC\_OVP and OVPGATE operation timings. The  $V_{VAC\_OVP}$  threshold can be set by  $l^2C$  serial interface. The adapter voltage must never exceed the absolute maximum rating of the VAC pin and the external OVPFET.

**Table 1. Fault Event List**

| FAULT EVENT      | CONDITIONS                                                                                                                                                                                                               | PROTECTION ACTION                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| AC_OVP           | $V_{VAC} > V_{VAC\_OVP}$ for $t_{VAC\_OVP\_DEG}$ during AC_PRESENT interval                                                                                                                                              | Turn off OVPFET and Q <sub>RB</sub> , enable R <sub>PD_VBUS</sub> , and reset CHG_MODE[2:0] to 000 |

| BUS_SC           | $V_{BUS}$ < 2V during BUS_INSERT interval or during OVPFET turn-on interval or reverse $I_{QRB}$ > 4A during switching or $V_{VBUS}$ < 1.9 × $V_{VOUT}$ in divider mode or $V_{VBUS}$ < 0.95 × $V_{VOUT}$ in bypass mode | Turn off OVPFET and $Q_{\text{RB}},$ and reset CHG_MODE[2:0] to $000$                              |

| VBUS_LO          | CHG_MODE[2:0] ≠ 000 (Off Mode)<br>(disabled after switching for 100s)                                                                                                                                                    | Charging initiation suspended                                                                      |

| VBUS_HI          | CHG_MODE[2:0] ≠000 (Off Mode)<br>(disabled after switching for 100s)                                                                                                                                                     | Charging initiation suspended                                                                      |

| BUS_OVP          | V <sub>VBUS</sub> > V <sub>BUS_OVP</sub> for t <sub>VBUS_OVP_DEG</sub> during BUS_INSERT interval                                                                                                                        | Turn off $Q_{RB}$ and reset CHG_MODE[2:0] to $000$                                                 |

| IBUS_OCP         | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off $Q_{RB}$ and reset CHG_MODE[2:0] to $000$                                                 |

| IBUS_UCP         | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| IBUS_UCP_TIMEOUT | I <sub>BUS</sub> < I <sub>BUS_UCP_R</sub> after 100s timeout                                                                                                                                                             | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| BAT_OVP          | $V_{BAT} > V_{BAT\_OVP}$ for $t_{VBAT\_OVP\_DEG}$ during BAT_INSERT interval                                                                                                                                             | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| IBAT_OCP         | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| VOUT_SC          | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| CFLY_SC          | CHG_MODE[2:0] = 010 (Voltage Divider Mode)                                                                                                                                                                               | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| CONV_OCP         | CHG_MODE[2:0] = 010 (Voltage Divider Mode)                                                                                                                                                                               | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| VDRP_OVP         | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| REG_TIMEOUT      | CHG_MODE[2:0] ≠ 000 (Off Mode)                                                                                                                                                                                           | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

| TDIE_OTP         | CHG_MODE[2:0] ≠ 000 (Off Mode) or ADC_EN = 1                                                                                                                                                                             | Turn off Q <sub>RB</sub> and reset CHG_MODE[2:0] to 000                                            |

Figure 8. AC\_OVP and OVPGATE Operation Timings

#### Input Short-Circuit Protection (BUS\_SC)

The BUS\_SC function monitors the VBUS pin for short-circuit. This function is enabled if the external OVPFET is turned on or if  $V_{VBUS}$  rises above  $V_{BUS\_PRESENT\_R}$ . If the  $V_{VBUS}$  falls below 2V (BUS\_SC event), the OVPFET is turned off, and charging is stopped. CHG\_MODE[2:0] bits are reset to 000 (disable). Also, BUS\_ABSENT\_FLAG bit is set to 1, and an INT pulse is asserted. The device will wait for 650ms before automatically re-enabling and initiating startup sequence.

During charging, if  $V_{VBUS}$  is less than 1.9 ×  $V_{VOUT}$  in divider mode or 0.95 ×  $V_{VOUT}$  in bypass mode, or if the  $Q_{RB}$  reverse current rises above 4A, the  $Q_{RB}$  and OVPFET are turned off, and charging is stopped. CHG\_MODE[2:0] bits are reset to 000 (disable). Also, BUS\_ABSENT\_FLAG bit is set to 1, and an INT pulse is asserted.

# VBUS Charge Voltage Range (VBUS\_LO and VBUS\_HI)

The VBUS\_LO and VBUS\_HI functions are included to avoid problems due to wrong V<sub>BUS</sub> setting for charging. Under no charge condition if V<sub>VBUS</sub> is less than (V<sub>VOUT</sub> × V<sub>BUS\_LO</sub> × 2) or above (V<sub>VOUT</sub> × V<sub>BUS\_HI</sub> × 2), the device remains in charge initiation operation if the voltage divider mode is selected. If the bypass mode is selected, the range is from (V<sub>VOUT</sub> × V<sub>BUS\_LO</sub>) to (V<sub>VOUT</sub> × V<sub>BUS\_HI</sub>). Charging will start once V<sub>BUS</sub> is within the charge range. VBUS\_LO and VBUS\_HI functions are enabled for maximum 100s at startup and are disabled if  $I_{BUS}$  is above  $I_{BUS\_UCP_R}$  during a period of 100s. The VBUS\_LO and VBUS\_HI thresholds can be set by  $I^2C$  serial interface.

# Input and Battery Over-Voltage Protections (BUS OVP and BAT OVP)

The BUS\_OVP and BAT\_OVP functions detect input and output charge voltage conditions. If either input or output voltage is higher than the protection threshold, the charger is turned off and CHG\_MODE[2:0] bits are reset to 000 (disable). The BUS\_OVP function monitors VBUS pin voltage. The BAT\_OVP uses BATP and BATN/SRP remote sense pins to monitor differential voltage between the battery terminals. To minimize the risk of battery terminal short in the manufacturing process, a series  $100\Omega$  resistor on the BATP pin is required. The BUS\_OVP and BAT\_OVP thresholds can be set by  $I^2C$  serial interface.

# Input and Battery Over-Current Protections (IBUS\_OCP and IBAT\_OCP)

The IBUS\_OCP function monitors the input current via  $Q_{RB}$ . If CHG\_MODE[2:0] bits are set to enable charge, the  $Q_{RB}$  is

turned on and the IBUS\_OCP function starts detecting the input current. If the  $I_{BUS}$  reaches  $I_{BUS\_OCP}$  threshold, the device stops charging and resets CHG\_MODE[2:0] bits to 000 (disable). The battery current is monitored by the voltage across an external  $5m\Omega$  series shunt resistor. This differential voltage is measured between BATN/SRP and SRN pins. If  $I_{BAT\_OCP}$  threshold is reached, the device stops charging and resets CHG\_MODE[2:0] bits to 000 (disable). The IBUS\_OCP and IBAT\_OCP thresholds can be set by  $I^2C$  serial interface.

#### Input Under-Current Protection (IBUS\_UCP)

The IBUS\_UCP function detects the input current via  $Q_{RB}$ . After charging is started, a 100s timer is enabled and  $I_{BUS}$  current is compared with  $I_{BUS\_UCP\_R}$  (selected by the IBUS\_UCP bit). If  $I_{BUS}$  cannot exceed  $I_{BUS\_UCP\_R}$  within the 100s period, the charging will be stopped and CHG\_MODE[2:0] bits are reset to 000 (disable). If  $I_{BUS}$  exceeds  $I_{BUS\_UCP\_R}$  within the 100s period, the timer is stopped and from then, if  $I_{BUS}$  falls below the  $I_{BUS\_UCP\_F}$  threshold, the charging will be stopped and CHG\_MODE[2:0] bits are reset to 000 (disable).

#### **VOUT Short-Circuit Protection (VOUT\_SC)**

The VOUT\_SC function monitors the VOUT pin for short-circuit. This function is enabled during charging. If  $V_{VOUT}$  falls below  $V_{VBUS}/2.28$  threshold when the voltage divider mode is selected, the charger is turned off and CHG\_MODE[2:0] bits are reset to 000 (disable). Also, the PIN\_DIAG\_FLAG bit is set to 1, and an INT pulse is generated. When the bypass mode is selected, the threshold is  $V_{VBUS}/1.14$ .

#### **CFLY Short-Circuit Protection (CFLY\_SC)**

The CFLY SC function identifies the health of flying capacitors before and during voltage divider switching (charging). The device initialization process is started after CHG\_MODE[2:0] bits are set to 010. When  $V_{\text{BUS}}$  is in the charge range, the flying capacitors (C<sub>FLY</sub>) in both phases are pre-charged. A CFLY short-circuit is detected if they cannot be charged, and the voltage between  $V_{\text{CFHx}}$  and  $V_{\text{CFLx}}$ remains below 2V. If so, the initialization process is stopped and CHG\_MODE[2:0] bits are reset to 000 (disable). Even if C<sub>FLY</sub> capacitors pass the short-circuit test in the initialization process, the CFLY SC function remains active and whenever a V<sub>CFLY</sub> voltage falls below 2V, the charger is turned off and CHG\_MODE[2:0] bits are reset to 000 (disable). The PIN DIAG FLAG bit is set to 1 and an INT pulse is generated as well. During a CFLY SC event, other protection events such as IBUS\_OCP, BAT\_OVP or CONV\_OCP may occur.

A CFLY discharge circuit is activated before the internal RBFET ( $Q_{RB}$ ) is turned on if  $V_{VBUS} > V_{BUS\_PRESENT\_R}$  to prevent over-current stress at the start of charging.

#### Converter Over-Current Protection (CONV\_OCP)

The CONV\_OCP function monitors the converter switch operating currents. If the  $Q_{CHx}$  and  $Q_{DLx}$  currents reach switch OCP threshold during voltage divider mode, the CONV\_OCP\_FLAG bit is set to 1, an INT pulse is generated, the charging is stopped, and CHG\_MODE[2:0] bits are reset to 000 (disable).

# Battery Voltage and Current Regulation (VBAT\_REG and IBAT\_REG)

The SGM41600 has VBAT\_REG and IBAT\_REG regulation functions to regulate the battery voltage and current for a short period before the system can re-adjust the conditions such that these functions can be disabled. The regulation thresholds can be set by I<sup>2</sup>C serial interface.

The VBAT\_REG function monitors the differential voltage between BATP and BATN/SRP pins and if the battery voltage is above the  $V_{BAT\_REG}$  threshold, the OVPGATE voltage is controlled to regulate the battery voltage.

The VBAT\_REG\_FLAG bit is also set to 1, and an INT pulse is generated. Then the host can negotiate with the adapter to reduce the current. This will gradually reduce the current until the bus current falls to the  $I_{\text{BUS}}$  UCP  $_{\text{F}}$  and charging will end.

Similarly, the IBAT\_REG function monitors the differential voltage between BATN/SRP and SRN pins to find the battery

current and if the  $I_{\text{BAT\_REG}}$  threshold is exceeded, the OVPGATE voltage is controlled (reduced) to regulate the charge current.

If one of the regulation functions is triggered and persist for 650ms when REG\_TIMEOUT\_DIS bit is set to 0, the charging will be stopped and CHG\_MODE[2:0] bits are reset to 000 (disable). The system should adjust the charging conditions to prevent the battery voltage and current regulation for more than 650ms (or prevent triggering of the VDRP\_OVP).

#### **Dropout Over-Voltage Protection (VDRP\_OVP)**

When VBAT\_REG or IBAT\_REG is active, a large voltage drop may appear on the external OVPFET and cause excessive power loss and heat. To avoid that, the VDRP\_OVP function monitors the voltage drop between VAC and VBUS pins. If it is higher than  $V_{DRP_OVP}$  threshold for  $t_{DRP_OVP_DEG}$  deglitch time (set by VDRP\_OVP\_DEG bit in REG0x05), the charging will be stopped and CHG\_MODE[2:0] bits are reset to 000 (disable). The  $V_{DRP_OVP}$  threshold and  $t_{DRP_OVP_DEG}$  deglitch time can be programmed by I²C serial interface.

#### Die Over-Temperature Protection (TDIE\_OTP)

The TDIE\_OTP function prevents charging in over-temperature condition. The die temperature is monitored and if the +150°C threshold is reached, the charging is stopped and CHG\_MODE[2:0] bits are reset to 000 (disable). An automatic startup sequence can initiate if the die temperature falls below +130°C.

# **REGISTER MAP**

All registers are 8-bit and individual bits are named from D[0] (LSB) to D[7] (MSB).

# I<sup>2</sup>C Slave Address of SGM41600 is: 0x6F (0b1101111 + W/R)

| FUNCTION                       | FLAG    | MASK    | THRESHOLD<br>SETTING  | ENABLE       | DEGLITCH |

|--------------------------------|---------|---------|-----------------------|--------------|----------|

| REG_RST                        | _       | _       | 0x00[7]               | _            | _        |

| CHG_MODE                       | _       | _       | 0x00[6:4]             | _            | _        |

| WD_TIMEOUT                     | 0x0F[5] | 0x10[5] | 0x00[2:0]             | 0x00[3]      | _        |

| FSW_SET                        | _       | _       | 0x01[7:5]             | _            | _        |

| FSW_SHIFT                      | _       | _       | 0x01[4:3]             | _            | _        |

| PIN_DIAG (CFLY_SC and VOUT_SC) | 0x0F[0] | 0x10[0] |                       | 0x02[7]      | _        |

| VBUS_LO                        | 0x0D[2] | 0x0E[2] | 0x02[3:2]             | 0x02[5]      | _        |

| VBUS_HI                        | 0x0D[1] | 0x0E[1] | 0x02[1:0]             | 0x02[4]      | _        |

| BUS_SC and BUS_ABSENT          | 0x0F[3] | 0x10[3] | 0x01[0]               | <del>-</del> | _        |

| DEVICE_REV                     | _       | _       | 0x03[7:4]             | _            | _        |

| DEVICE_ID                      | _       | _       | 0x03[3:0]             | <del>-</del> | _        |

| AC_OVP                         | 0x0B[7] | 0x0C[7] | 0x04[3:0]             | 0x04[4]      | _        |

| AC_PDN                         | 0x0B[6] | 0x0C[6] | _                     | 0x05[7]      | _        |

| BUS_PDN                        | 0x0B[5] | 0x0C[5] | _                     | 0x05[6]      | _        |

| VDRP_OVP                       | 0x0B[4] | 0x0C[4] | 0x05[2:0]             | 0x05[5]      | 0x05[4]  |

| BUS_OVP                        | 0x0B[3] | 0x0C[3] | 0x06[6:0]             | 0x06[7]      | _        |

| IBUS_OCP                       | 0x0B[2] | 0x0C[2] | 0x07[4:0]             | 0x07[5]      | _        |

| IBUS_UCP_RISE                  | 0x0B[1] | 0x0C[1] | 0x07[6]               | 0x07[7]      | _        |

| IBUS_UCP_FALL                  | 0x0B[0] | 0x0C[0] | 0x07[6]               | 0x07[7]      | _        |

| IBUS_UCP_TIMEOUT               | 0x0F[2] | 0x10[2] | _                     | _            | _        |

| BAT_OVP                        | 0x0D[7] | 0x0E[7] | 0x08[5:0]             | 0x08[7]      | _        |

| IBAT_OCP                       | 0x0D[6] | 0x0E[6] | 0x09[5:0]             | 0x09[7]      | _        |

| VBAT_REG                       | 0x0D[5] | 0x0E[5] | 0x0A[1:0]             | 0x0A[2]      | _        |

| IBAT_REG                       | 0x0D[4] | 0x0E[4] | 0x0A[4:3]             | 0x0A[5]      | _        |

| REG_TIMEOUT                    | _       | _       | _                     | 0x0A[6]      | _        |

| TDIE_OTP                       | 0x0D[3] | 0x0E[3] | _                     | _            | _        |

| CONV_OCP                       | 0x0D[0] | 0x0E[0] | 0x01[1]               | _            | _        |

| BUS_INSERT                     | 0x0F[7] | 0x10[7] | _                     | _            | _        |

| BAT_INSERT                     | 0x0F[6] | 0x10[6] | _                     |              | _        |

| AC_ABSENT                      | 0x0F[4] | 0x10[4] | _                     | _            | _        |

| ADC_DONE                       | 0x0F[1] | 0x10[1] | _                     | _            | _        |

| ADC_EN                         | _       | _       | _                     | 0x11[7]      | _        |

| ADC_RATE                       | _       | _       | 0x11[6]               |              | _        |

| VBUS_ADC                       |         | _       | 0x12[3:0] + 0x13[7:0] | 0x11[5]      | _        |

| IBUS_ADC                       |         |         | 0x14[3:0] + 0x15[7:0] | 0x11[4]      |          |

| VBAT_ADC                       |         | _       | 0x16[3:0] + 0x17[7:0] | 0x11[3]      |          |

| IBAT_ADC                       | _       | _       | 0x18[3:0] + 0x19[7:0] | 0x11[2]      | _        |

| TDIE_ADC                       | _       | _       | 0x1A[7:0]             | 0x11[1]      | _        |

Bit Types:

R: Read only R/W: Read/Write

RC: Read clears the bit

R/WC: Read/Write. Writing a '1' clears the bit. Writing a '0' has no effect.

### **REG0x00: CONTROL1 Register Address [reset = 0x00]**

| BITS   | BIT NAME       | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                            | RESET BY                                        |

|--------|----------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| D[7]   | REG_RST        | 0       | R/W  | Register Reset 0 = No register reset (default) 1 = Reset all registers to their default values                                                                                                         | REG_RST                                         |

| D[6:4] | CHG_MODE[2:0]  | 000     | R/W  | Charge Mode Control 000 = Off mode (default) 001 = Forward bypass mode 010 = Forward charge-pump voltage divider mode 011 ~ 111 = Off mode Note: These bits are not allowed to change during charging. | REG_RST,<br>Watchdog or<br>many other<br>events |

| D[3]   | WDT_DIS        | 0       | R/W  | Watchdog Enable 0 = Watchdog enabled (default) 1 = Watchdog disabled                                                                                                                                   | REG_RST                                         |

| D[2:0] | WDT_TIMER[2:0] | 000     | R/W  | Watchdog Timer Setting 000 = 0.5s (default) 001 = 1s 010 = 2s 011 = 5s 100 = 10s 101 = 20s 111 = 40s 111 = 80s                                                                                         | REG_RST                                         |

### **REG0x01: CONTROL2 Register Address [reset = 0x42]**

| BITS   | BIT NAME       | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                            | RESET BY |

|--------|----------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7:5] | FSW_SET[2:0]   | 010     | R/W  | Voltage Divider Switching Frequency Setting 000 = 200kHz 001 = 375kHz 010 = 500kHz (default) 011 = 750kHz 100 = 1000kHz 101 = 1250kHz 110 ~ 111 = 1500kHz                                                                                              | NA       |

| D[4:3] | FSW_SHIFT[1:0] | 00      | R/W  | Trimming Bits for Switching Frequency (for EMI frequency spectrum shifting) 00/11 = Nominal frequency (default) 01 = Nominal frequency + 10% 10 = Nominal frequency - 10%                                                                              | REG_RST  |

| D[2]   | Reserved       | 0       | R    | Reserved                                                                                                                                                                                                                                               | NA       |

| D[1]   | CONV_OCP       | 1       | R/W  | CONV OCP Threshold Setting Bit<br>0 = 7.3A<br>1 = 5.6A (default)                                                                                                                                                                                       | NA       |

| D[0]   | BUS_SC_TRG     | 0       | R/W  | Setting Bit of VBUS Short-Circuit Trigger Mode during Switching 0 = Triggered by Q <sub>RB</sub> 4A reverse current (default) 1 = Triggered by V <sub>VBUS</sub> /V <sub>OUT</sub> scale factor, 1.9 in voltage divider mode while 0.95 in bypass mode | NA       |

# REG0x02: CONTROL3 Register Address [reset = 0xBC]

| BITS   | BIT NAME     | DEFAULT | TYPE | DESCRIPTION                                                                                       | RESET BY |

|--------|--------------|---------|------|---------------------------------------------------------------------------------------------------|----------|

| D[7]   | PIN_DIAG_EN  | 1       | R/W  | Pin Diagnosis Enable 0 = Disabled 1 = Enabled (default)                                           | REG_RST  |

| D[6]   | Reserved     | 0       | R    | Reserved                                                                                          | NA       |

| D[5]   | VBUS_LO_EN   | 1       | R/W  | Low VBUS Error Detection Enable 0 = Disabled 1 = Enabled (default)                                | REG_RST  |

| D[4]   | VBUS_HI_EN   | 1       | R/W  | High VBUS Error Detection Enable 0 = Disabled 1 = Enabled (default)                               | REG_RST  |

| D[3:2] | VBUS_LO[1:0] | 11      | R/W  | Low VBUS Error Range Scale Setting<br>00 = 1.01<br>01 = 1.02<br>10 = 1.03<br>11 = 1.04 (default)  | NA       |

| D[1:0] | VBUS_HI[1:0] | 00      | R/W  | High VBUS Error Range Scale Setting<br>00 = 1.10 (default)<br>01 = 1.15<br>10 = 1.20<br>11 = 1.25 | NA       |

### **REG0x03: DEVICE\_INFO Register Address [reset = 0x08]**

| BITS   | BIT NAME        | DEFAULT | TYPE | DESCRIPTION                  | RESET BY |

|--------|-----------------|---------|------|------------------------------|----------|

| D[7:4] | DEVICE_REV[3:0] | 0000    | R    | Device Revision              | NA       |

| D[3:0] | DEVICE_ID[3:0]  | 1000    | R    | Device ID<br>1000 = SGM41600 | NA       |

### REG0x04: AC\_OVP Register Address [reset = 0x18]

| BITS   | BIT NAME    | DEFAULT | TYPE | DESCRIPTION                                                                                                                                               | RESET BY |

|--------|-------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[7:5] | Reserved    | 000     | R    | Reserved                                                                                                                                                  | NA       |

| D[4]   | AC_OVP_EN   | 1       | R/W  | VAC OVP Enable 0 = Disabled 1 = Enabled (default)                                                                                                         | REG_RST  |

| D[3:0] | AC_OVP[3:0] | 1000    | R/W  | VAC OVP Rising Threshold Setting  VAC OVP Rising Threshold Value: = 4V + AC_OVP[3:0] × 1V  Offset: 4V  Range: 4V (0000) - 19V (1111)  Default: 12V (1000) | REG_RST  |

# REG0x05: Pull-Down & VDRP\_OVP Register Address [reset = 0x25]

| BITS   | BIT NAME      | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                                                                                               | RESET BY |

|--------|---------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|