#### **GENERAL DESCRIPTION**

The XRP6670 is a synchronous current mode PWM step-down (buck) regulator capable of delivering up to 3 Amps. A 2.6V to 5.5V input voltage range allows for single supply operation from industry standard 3.3V and 5V power rails.

Based on a current mode PWM control scheme, the XRP6670 operating frequency is programmable between 300kHz and 2.5MHz via an external resistor. This flexibility allows the XRP6670 to optimize component selection and reduce component count and solution footprint. It provides a low output voltage ripple, excellent line and load regulation and has a 100% duty cycle LDO mode. Output voltage is adjustable to as low as 0.8V with a better than 2% accuracy while a low quiescent current supports the most stringent battery operating conditions.

Built-in over-temperature, overcurrent, short circuit and under-voltage lock-out protections insure safe operations under abnormal operating conditions.

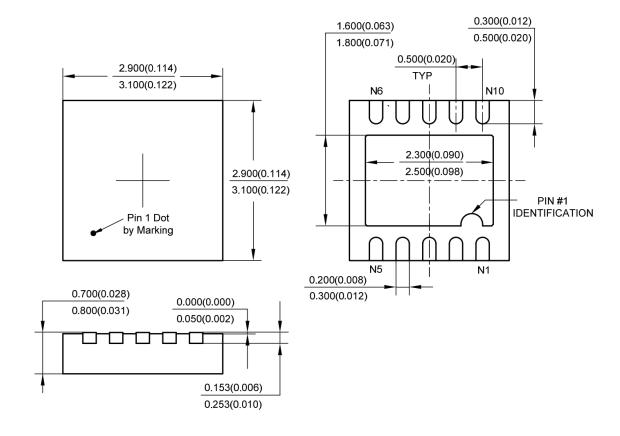

The XRP6670 is offered in a RoHS compliant, "green"/halogen free 3mmx3mm 10-pin DFN package.

#### **APPLICATIONS**

- Industrial & Medical Equipment

- Audio-Video Equipment

- Networking & Telecom Equipment

- Portable/Battery Operated Equipment

### **FEATURES**

- Guaranteed 3A Output Current

- Input Voltage: 2.6V to 5.5V

- Prog. PWM Current Mode Control

- Programmable 300kHz to 2.5MHz

- 100% Duty Cycle LDO Mode Operation

- Achieves 95% Efficiency

- Adjustable Output Voltage Range

- 0.8V to 5V with ±2% Accuracy

- Enable and Power Good Functions

- 460µA Quiescent Current

- Over-temperature, Over-current, Short-circuit and UVLO Protections

- RoHS Compliant "Green"/Halogen Free 3mm x 3mm 10-Pin DFN Package

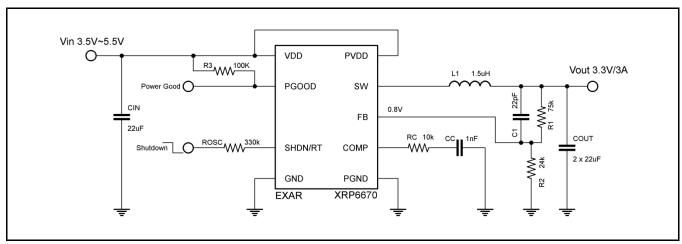

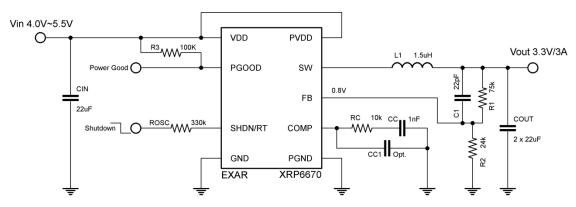

### TYPICAL APPLICATION DIAGRAM

Fig. 1: XRP6670 Application Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| V <sub>DD</sub> , PV <sub>DD</sub> , FB, COMP, SHDN/RT    | 0.3V to 6.0V                   |

|-----------------------------------------------------------|--------------------------------|

| SW                                                        | -0.3V to V <sub>DD</sub> +0.3V |

| Junction Temperature Range                                | +150°C                         |

| Storage Temperature                                       | 65°C to 150°C                  |

|                                                           |                                |

| Power Dissipation                                         | . Internally Limited           |

| Power Dissipation<br>Lead Temperature (Soldering, 10 sec) | •                              |

| ·                                                         | 260°C                          |

### **OPERATING RATINGS**

| Input Voltage Range V <sub>IN</sub> | 2.6V to 5.5V   |

|-------------------------------------|----------------|

| Maximum Output Current (Min.)       | 3A             |

| Junction Temperature Range          | 40°C to +125°C |

| Thermal Resistance                  |                |

| DFN10 θ <sub>JA</sub>               | 110°C/W        |

| DFN10 θ <sub>JC</sub>               | 3°C/W          |

Note 1:  $T_1$  is a function of the ambient temperature  $T_A$  and power dissipation  $P_D$ :  $(T_1 = T_A + (P_D * \theta_{JA}))$

### **ELECTRICAL SPECIFICATIONS**

Specifications are for an Operating Junction Temperature of  $T_A = T_J = 25^{\circ}\text{C}$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise indicated,  $V_{DD} = V_{PVDD} = 3.3V$ ,  $T_A = T_J = 25^{\circ}\text{C}$ .

| Parameter                                  | Min.  | Тур.                 | Max.                 | Units | Conditions                                       |

|--------------------------------------------|-------|----------------------|----------------------|-------|--------------------------------------------------|

| Supply Current                             |       | 460                  |                      | μA    | V <sub>FB</sub> =0.75V, No switching             |

| Shutdown Supply Current                    |       |                      | 1                    | μA    | SHDN/RT=V <sub>DD</sub> =V <sub>PVDD</sub> =5.5V |

| Under Voltage Lockout (UVLO)<br>Threshold  |       | 2.2                  |                      | V     | V <sub>DD</sub> rising                           |

| Under Voltage Lockout (UVLO)<br>Hysteresis |       | 300                  |                      | mV    |                                                  |

| Feedback Voltage V <sub>FB</sub>           | 0.784 | 0.800                | 0.816                | V     |                                                  |

| FB Pin Bias Current                        |       | 0.1                  | 0.4                  | μΑ    |                                                  |

| Current Sense Transresistance              |       | 0.2                  |                      | Ω     |                                                  |

| Switching Leakage Current                  |       |                      | 1                    | μΑ    | SHDN/RT=V <sub>DD</sub> =5.5V                    |

| Error Amplifier Voltage Gain               |       | 800                  |                      | V/V   |                                                  |

| Error Amplifier Trans-<br>conductance      |       | 800                  |                      | μA/V  |                                                  |

| RT Pin Voltage                             | 0.760 | 0.800                | 0.840                | V     |                                                  |

| Cuitching Fraguency Dange                  | 0.3   |                      | 2.5                  | MHz   | Programmed via Rosc                              |

| Switching Frequency Range                  | 0.8   | 1                    | 1.2                  |       | $R_{OSC}$ =330 $k\Omega$                         |

| Maximum Duty Cycle                         | 100   |                      |                      | %     | V <sub>FB</sub> =0.75V                           |

| Minimum On-Time                            |       | 120                  | 150                  | ns    |                                                  |

| Switch Current Limit                       | 3.2   | 4.2                  |                      | Α     | V <sub>FB</sub> =0.75V                           |

| Switching FET On Resistance                |       | 0.11                 | 0.16                 | Ω     | I <sub>sw</sub> =500mA                           |

| Synchronous FET On Resistance              |       | 0.11                 | 0.17                 | Ω     | I <sub>sw</sub> =500mA                           |

| Shutdown Threshold                         |       | V <sub>DD</sub> -0.7 | V <sub>DD</sub> -0.4 | V     |                                                  |

| PGOOD Voltage Range                        | -15   |                      | +15                  | %     |                                                  |

| PGOOD Pull Down Resistance                 |       |                      | 120                  | Ω     |                                                  |

| Output Current                             | 3     |                      |                      | Α     | $V_{DD}$ = 2.6V to 5.5V, $V_{OUT}$ = 2.5V        |

| Output Voltage Line Regulation             |       | 0.4                  |                      | %/V   | $V_{DD}$ = 2.7V to 5.5V, $I_{OUT}$ = 100mA       |

| Output Voltage Load Regulation             |       | ±0.2                 |                      | %     | I <sub>OUT</sub> = 10mA to 3A                    |

| Soft Start Time                            |       | 1.5                  |                      | ms    | I <sub>OUT</sub> = 10mA                          |

| Thermal Shutdown Temperature               |       | 160                  |                      | °C    |                                                  |

| Thermal Shutdown Hysteresis                |       | 20                   |                      | °C    |                                                  |

2/13 Rev. 1.0.2

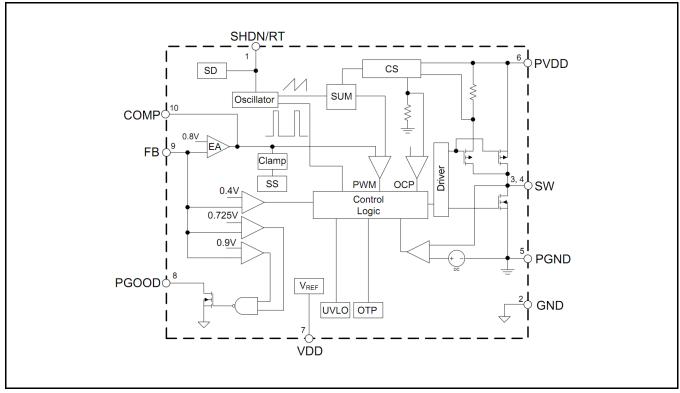

## **BLOCK DIAGRAM**

Fig. 2: XRP6670 Block Diagram

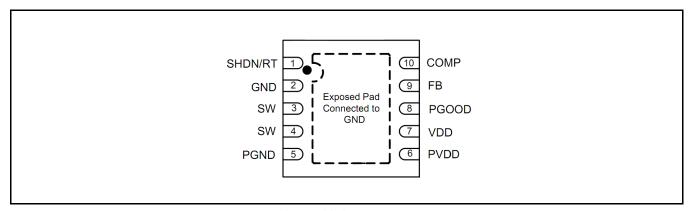

## **PIN ASSIGNMENT**

Fig. 3: XRP6670 Pin Assignment

## **PIN DESCRIPTION**

| Name     | Pin Number | Description                                                                                                                                                                                              |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHDN/RT  | 1          | Shutdown and Oscillator resistor input. Connect a resistor to GND from this pin to set the switching frequency. Forcing this pin to VDD shuts down the device.                                           |

| GND      | 2          | Signal ground. All small-signal ground, such as the compensation components and exposed pad should be connected to this, which in turn connects to PGND at one point.                                    |

| SW       | 3, 4       | Power switch output pin. This pin is connected to the inductor.                                                                                                                                          |

| PGND     | 5          | Power Ground Signal. Connect this signal as close as possible to the input and output capacitors $C_{\text{IN}}$ and $C_{\text{OUT}}$ .                                                                  |

| PVDD     | 6          | Power Input Supply Pin. Decouple this pin to PGND (pin 5) with a capacitor.                                                                                                                              |

| VDD      | 7          | Signal Input Supply Pin. Decouple this pin to GND (pin 2) with a capacitor. Typically, VDD and PVDD are connected together.                                                                              |

| PGOOD    | 8          | Power Good Flag. This is an open drain output and is pulled to ground if the output voltage is out of regulation.                                                                                        |

| FB       | 9          | Feedback pin. An external resistor divider connected to FB programs the output voltage.                                                                                                                  |

| СОМР     | 10         | Compensation pin. This is the output of transconductance error amplifier and the input to the current comparator. It is used to compensate the control loop. Connect an RC network form this pin to GND. |

| Exp. Pad | Exp. Pad   | Connect to GND signal (pin 2).                                                                                                                                                                           |

## ORDERING INFORMATION(1)

| Part Number   | Junction Temperature Range      | Package | Packing Method | Lead Free <sup>(2)</sup> |

|---------------|---------------------------------|---------|----------------|--------------------------|

| XRP6670EHTR-F | -40°C ≤ T <sub>J</sub> ≤ +125°C | DFN10   | Tape & Reel    | Yes                      |

| XRP6670EVB    | XRP6670 Evaluation Board        |         |                |                          |

Notes:

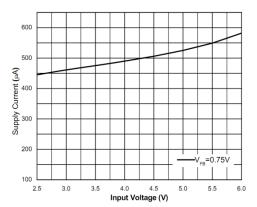

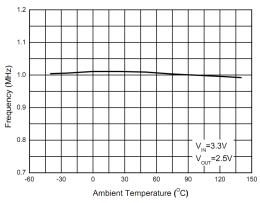

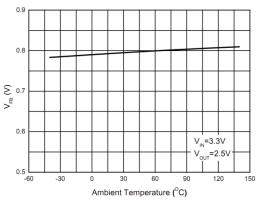

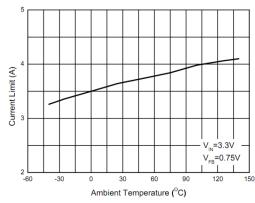

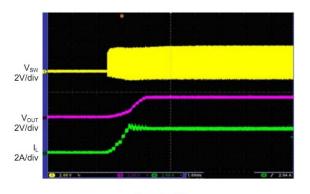

### TYPICAL PERFORMANCE CHARACTERISTICS

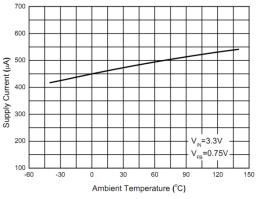

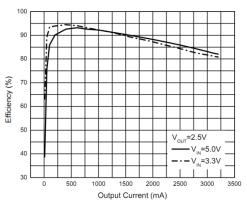

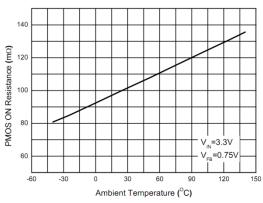

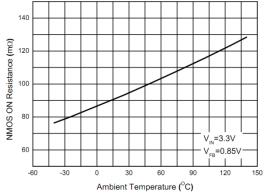

All data taken at  $V_{\text{IN}} = V_{\text{DD}} = V_{\text{PVDD}} = 3.3V$ ,  $T_{\text{J}} = T_{\text{A}} = 25^{\circ}\text{C}$ , unless otherwise specified - Schematic and BOM from Application Information section of this datasheet.

Fig. 4: Supply Current Versus Input Voltage

Fig. 5: Supply Current versus Ambient Temperature

Fig. 6: Efficiency versus Output Current

Fig. 7: PMOS RDS<sub>ON</sub> Resistance versus Ambient Temperature

Fig. 8: NMOS RDS<sub>ON</sub> Resistance versus Ambient Temperature

Fig. 9: Frequency versus Ambient Temperature

Fig. 10: V<sub>FB</sub> versus Ambient Temperature

Fig. 11: Current Limit versus Ambient Temperature

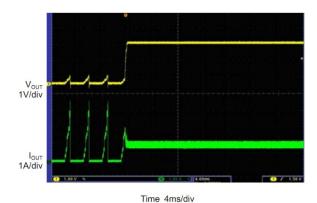

$\label{eq:fig:fine_fine_fine_fine} \begin{tabular}{ll} Time & 1ms/div \\ Fig. 12: & Start-up & from VIN \\ V_{IN}{=}3.3V, & V_{OUT}{=}2.5V, & I_{OUT}{=}3A \\ \end{tabular}$

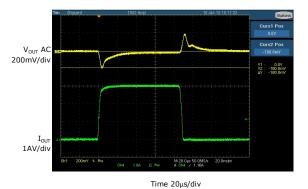

Fig. 13: Load Transient Response  $V_{IN}$ =5V,  $V_{OUT}$ =2.5V,  $I_{OUT}$ =0A to 3A

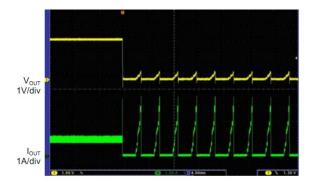

Fig. 15: Short Circuit Recovery  $V_{IN}=3.3V$ ,  $V_{OUT}=2.5V$

#### THEORY OF OPERATION

#### **FUNCTIONAL DESCRIPTION**

The XRP6670 is a synchronous, current-mode, step-down regulator. It regulates input voltages from 2.6V to 5.5V and supplies up to 3A of output current  $I_{OUT}$ . The XRP6670 uses current-mode control to regulate the output voltage Vout. The Vout is measured at FB through a resistive voltage divider and input to a transconductance error amplifier. The highside switch current is compared to the output of the error amplifier to control the output voltage. The regulator utilizes internal Pchannel and N-channel MOSFETs to step-down the input voltage. Because the high-side FET is P-channel a bootstrapping capacitor is not necessary and the regulator can operate at 100% duty cycle. The XRP6670 has several powerful protection features including OCP, OTP, UVLO and output short-circuit.

# SHORT-CIRCUIT AND OVER-CURRENT PROTECTION OCP

The XRP6670 protects itself and downstream circuits against accidental increase in current or short-circuit. If peak current through the switching FET increases above 4.2A (nominal) the regulator enters an idle state where the internal FETs are turned off and softstart is pulled low. After a period of 2000xT the regulator will attempt a softstart. If the high current persists the protection cycle will repeat.

#### **SOFT-START**

XRP6670 has an integrated soft-start which is preset at 1.5ms (nominal). This feature limits the inrush current during startup and allows the output voltage to smoothly rise to its programmed value.

#### **APPLICATION INFORMATION**

#### PROGRAMMING THE OUTPUT VOLTAGE

Use an external resistor divider to set the output voltage based on the following equation:

#### **POWER GOOD FLAG**

This open drain output (PGOOD) can be used to monitor whether the output voltage is within regulation ( $\pm 15\%$ ). PGOOD is pulled to ground when V<sub>OUT</sub> is not in regulation. PGOOD should be tied to VDD with a 100k resistor.

### PROGRAMMABLE FREQUENCY

The switching frequency is programmable within a range of 300kHz to 2.5MHz via a resistor placed between SHDN/RT and GND pins. An equation for calculating a resistor value for a target frequency is given the Application Information section.

#### 100% DUTY CYCLE AND LDO OPERATION

The XRP6670 switching FET is a P-channel device and therefore can operate at 100% duty cycle. In battery operated applications where  $V_{\rm IN}$  will droop, XRP6670 can seamlessly transition from PWM to LDO mode.

#### **OVER-TEMPERATURE PROTECTION OTP**

If the junction temperature exceeds 160°C the OTP circuit is triggered, turning off the internal control circuit and FETs. When junction temperature drops below 140°C the XRP6670 will restart.

Although thermal shutdown is built-in in the XRP6670 to protect the device from thermal damage, the total power dissipation that the XRP6670 can sustain is based on the package thermal capability. Equation 1 shown on page two, can be used to calculate junction temperature and ensure operation within the recommended maximum temperature of 125°C.

$$R2 = \frac{R1}{\left(\frac{V_{OUT}}{0.800V} - 1\right)}$$

Where:

R1 is the resistor between  $V_{\text{OUT}}$  and FB (nominally set at  $100k\Omega)$

R2 is the resistor between FB and GND

0.800V is the nominal feedback voltage

A resistor selection guide for common values of  $V_{\text{OUT}}$  is shown in table 1.

| VOUT | R1(kΩ) | R2(kΩ) |

|------|--------|--------|

| 1.1V | 100    | 267    |

| 1.2V | 100    | 200    |

| 1.5V | 105    | 120    |

| 1.8V | 120    | 95.3   |

| 2.5V | 100    | 47     |

| 2.8V | 75     | 30     |

| 3.3V | 75     | 24     |

Table 1: Resistor Selection

### PROGRAMMING THE FREQUENCY

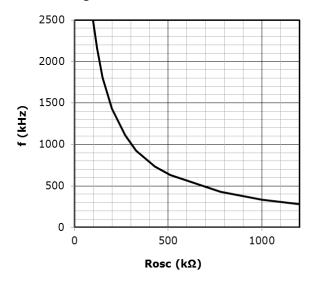

Use resistor Rosc between SHDN/RT and GND pins to program the switching frequency. A graph of nominal frequency versus Rosc is shown in figure 16.

Fig. 16: Frequency versus Rosc

The following equation closely fits the empirical data and can be used to select Rosc for a given frequency.

$$R_{OSC} = \frac{9.28 \times 10^{11}}{f^{1.084}}$$

#### **DUTY-CYCLE LIMITATION**

XRP6670 has a "Minimum On-Time" specification of 150ns which imposes a restriction on minimum duty-cycle (see table 2)

| F (MHz) | T <sub>TYP</sub> (ns) | T <sub>MIN</sub> (ns) | Duty-cycle <sub>MIN</sub> |

|---------|-----------------------|-----------------------|---------------------------|

| 1.0     | 1000                  | 800                   | 0.19                      |

| 2.0     | 500                   | 400                   | 0.38                      |

Table 2: Minimum duty-cycle arising from "Minimum On-Time)

For example if frequency is set at 2MHz then typical switching period is 500ns. Allowing a  $\pm 20\%$  uncertainty, minimum period is 400ns and corresponding minimum duty-cycle is 0.38. Recall that for a buck regulator duty-cycle= $V_{OUT}/V_{IN}$ . Therefore when operating at 2MHz with  $V_{IN}$  of 5V, a  $V_{OUT} \le 1.9V$  is not possible (5V x 0.38 = 1.9V).

#### **OUTPUT INDUCTOR**

Select the output inductor for inductance L, DC current rating  $I_{DC}$  and saturation current rating  $I_{SAT}$ .  $I_{DC}$  should be larger than regulator output current.  $I_{SAT}$ , as a rule of thumb, should be 50% higher than the regulator output current. Since the regulator is rated at 3A then  $I_{DC} \ge 3A$  and  $I_{SAT} \ge 4.5A$ .

Please note that "Peak Switch Current" is rated at 3.2A minimum. Therefore applications that require an output current of 3A should limit the peak-to-peak inductor current ripple to  $\Delta I_L \leq 0.4A$ . In the following we will use the common practice of  $\Delta I_L \leq 1A$ . Therefore **worst-case** maximum output current will be limited to  $I_{OUT}=3.2A-0.5A=2.7A$ .

Calculate the inductance from:

$$L = (V_{IN} - V_{OUT}) \left( \frac{V_{OUT}}{\Delta I_I \times f_s \times V_{IN}} \right)$$

Where:

$\Delta I_L$  is peak-to-peak inductor current ripple nominally set to  $\leq\!30\%$  of  $I_{OUT}$

fs is nominal switching frequency

As an example, inductor values corresponding to  $5V_{IN}/1MHz$  and  $3.3V_{IN}/1MHz$  are shown in tables 3 and 4 for several common output

voltages. Note that example inductors shown in tables 3 and 4 are Wurth shielded inductors.

| VOUT(V) | $\Delta I_{L(p-p)}(A)$ | L(µH) | Inductor<br>Example |

|---------|------------------------|-------|---------------------|

| 3.3     | 0.76                   | 1.5   | 74437346015         |

| 2.8     | 0.81                   | 1.5   | 74437346015         |

| 2.5     | 0.84                   | 1.5   | 74437346015         |

| 1.8     | 0.76                   | 1.5   | 74437346015         |

| 1.5     | 0.70                   | 1.5   | 74437346015         |

| 1.2     | 0.62                   | 1.5   | 74437346015         |

| 1.1     | 0.57                   | 1.5   | 74437346015         |

Table 3: Suggested Inductor Values for f=1MHz,  $V_{IN}=5V$  and  $I_{OUT}=2.7A$

| VOUT(V) | ΔI <sub>L(p-p)</sub> (A) | L(µH) | Inductor<br>Example |

|---------|--------------------------|-------|---------------------|

| 2.5     | 0.41                     | 1.5   | 74437346015         |

| 1.8     | 0.54                     | 1.5   | 74437346015         |

| 1.5     | 0.54                     | 1.5   | 74437346015         |

| 1.2     | 0.51                     | 1.5   | 74437346015         |

| 1.1     | 0.49                     | 1.5   | 74437346015         |

Table 4: Suggested Inductor Values for f=1MHz,  $V_{IN}=3.3V$  and  $I_{OUT}=2.7A$

#### **OUTPUT CAPACITOR COUT**

Select the output capacitor for voltage rating, capacitance C<sub>OUT</sub> and Equivalent Resistance ESR. The voltage rating, as a rule of thumb, should be at least twice the output When calculating the required voltage. capacitance, usually the overriding requirement is current load-step transient. If the unloading transient (i.e., when load transitions from a high to a low current) is met, then usually the loading transient (when load transitions from a low to a high current) is met as well. Therefore calculate the Cout based on the unloading transient requirement from:

$$C_{OUT} = L \times \left(\frac{{I_{High}}^2 - {I_{Low}}^2}{(V_{OUT} + V_{transient})^2 - {V_{OUT}}^2}\right)$$

Where:

L is the inductance calculated in the preceding step

I<sub>High</sub> is the value of load-step prior to unloading. This is nominally set equal to regulator current rating (3A).

$I_{\text{Low}}$  is the value of load-step after unloading. This is nominally set equal to 50% of regulator current rating (1.5A).

$V_{transient}$  is the maximum permissible voltage transient corresponding to the load step mentioned above.  $V_{transient}$  is typically specified from 3% to 5% of  $V_{OUT}$ .

ESR of the capacitor has to be selected such that the output voltage ripple requirement  $\Delta V_{\text{OUT}},$  nominally 1% of  $V_{\text{OUT}},$  is met. Voltage ripple  $\Delta V_{\text{OUT}}$  is mainly composed of two components: the resistive ripple due to ESR and capacitive ripple due to  $C_{\text{OUT}}$  charge transfer. For applications requiring low voltage ripple, ceramic capacitors are recommended because of their low ESR which is typically in the range of  $5m\Omega.$  Therefore  $\Delta V_{\text{OUT}}$  is mainly capacitive. For ceramic capacitors calculate the  $\Delta V_{\text{OUT}}$  from:

$$\Delta V_{OUT} = \frac{\Delta I_L}{8 \times C_{OUT} \times f_s}$$

Where:

$\Delta I_L$  is from table 2 or 3

Cout is the value calculated above

fs is nominal switching frequency

If tantalum or electrolytic capacitors are used then  $\Delta V_{\text{OUT}}$  is essentially a function of ESR:

$$\Delta V_{OUT} = \Delta I_L \times ESR$$

#### INPUT CAPACITOR CTN

Select the input capacitor for voltage rating, RMS current rating and capacitance. The voltage rating should be at least 50% higher than the regulator's maximum input voltage. Calculate the capacitor's current rating from:

$$I_{CIN,RMS} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

Where:

$I_{OUT}$  is regulator's maximum current (3A) D is duty cycle (D= $V_{OUT}/V_{IN}$ )

Calculate the C<sub>IN</sub> capacitance from:

$$C_{IN} = \frac{I_{OUT} \times V_{OUT} \times (V_{IN} - V_{OUT})}{f_s \times {V_{IN}}^2 \times \Delta V_{IN}}$$

Where:

$\Delta V_{\text{IN}}$  is the permissible input voltage ripple, nominally set at 1% of  $V_{\text{IN}}$

#### **LOOP COMPENSATION**

XRP6670 utilizes current-mode control. This allows using a minimum of external components to compensate the regulator. In general only two components are needed: RC and CC. Proper compensation of the regulator (determining RC and CC) results in optimum transient response. In terms of power supply control theory, the goals of compensation are to choose RC and CC such that the regulator loop gain has a crossover frequency fc equal 10% of switching frequency. corresponding phase-margin should between 45 degrees and 65 degrees. An important characteristic of current-mode buck regulator is its dominant pole. The frequency of the dominant pole is given by:

$$f_p = \frac{1}{2\pi \times C_{OUT} \times R_{load}}$$

where R<sub>load</sub> is the output load resistance.

The uncompensated regulator has a constant gain up to its pole frequency, beyond which the gain decreases at  $-20 \, \text{dB/decade}$ . The zero arising from the output capacitor's ESR is inconsequential if ceramic  $C_{\text{OUT}}$  is used. This simplifies the compensation. The RC and CC, which are placed between the output of XRP6670's Error Amplifier and ground, constitute a zero. The frequency of this compensating zero is given by:

$$f_z = \frac{1}{2\pi \times RC \times CC}$$

For the typical application circuit shown in this datasheet, RC= $10k\Omega$  and CC=1nF provide a satisfactory compensation. Please use EXAR application note for compensating other application circuits.

### TYPICAL APPLICATIONS

### 5V to 3.3V conversion - 1MHz

Fig. 17: 3.5V-5.5V to 3.3V Conversion 1MHz Switching Operations

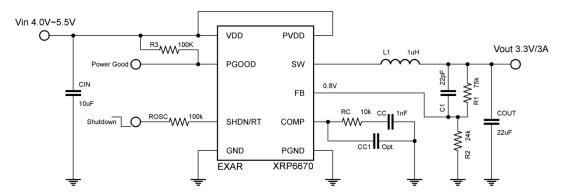

### **5V** TO **3.3V** CONVERSION - **2.5MHz**

Fig. 18: 4V-5.5V to 3.3V Conversion 2.5MHz Switching Operations

## **PACKAGE SPECIFICATION**

### **3MM X 3MM DFN-10**

## **REVISION HISTORY**

| Revision | Date       | Description                                              |

|----------|------------|----------------------------------------------------------|

| 1.0.0    | 03/19/2013 | Initial release of datasheet                             |

| 1.0.1    | 06/20/2013 | Corrected CC=1nF on page 10                              |

| 1.0.2    | 11/01/2019 | Updated to MaxLinear logo. Updated Ordering Information. |