# Low-Power, SC70/SOT µP Reset Circuits with Capacitor-Adjustable Reset Timeout Delay

#### **General Description**

The MAX6340/MAX6421–MAX6426 low-power microprocessor supervisor circuits monitor system voltages from 1.6V to 5V. These devices perform a single function: they assert a reset signal whenever the  $V_{CC}$  supply voltage falls below its reset threshold. The reset output remains asserted for the reset timeout period after  $V_{CC}$  rises above the reset threshold. The reset timeout is externally set by a capacitor to provide more flexibility.

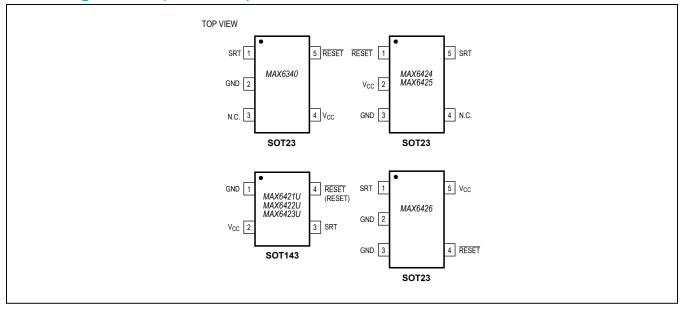

The MAX6421/MAX6424 have an active-low, push-pull reset output. The MAX6422 has an active-high, push-pull reset output and the MAX6340/MAX6423/ MAX6425/MAX6426 have an active-low, open-drain reset output. The MAX6421/MAX6422/MAX6423 are offered in 4-pin SC70 or SOT143 packages. The MAX6340/MAX6424/MAX6425/MAX6426 are available in 5-pin SOT23-5 packages.

#### **Applications**

- Portable Equipment

- Battery-Powered Computers/Controllers

- Automotive

- Medical Equipment

- Intelligent Instruments

- Embedded Controllers

- Critical µP Monitoring

- Set-Top Boxes

- Computers

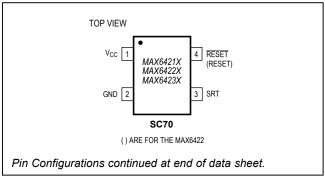

### **Pin Configurations**

#### **Benefits and Features**

- Monitor System Voltages from 1.6V to 5V

- Capacitor-Adjustable Reset Timeout Period

- Low Quiescent Current (1.6µA typ)

- Three RESET Output Options

Push-Pull RESET

Push-Pull RESET

Open-Drain RESET

- Guaranteed Reset Valid to V<sub>CC</sub> = 1V

- Immune to Short V<sub>CC</sub> Transients

- Small 4-Pin SC70, 4-Pin SOT143, and 5-Pin SOT23 Packages

- MAX6340 Pin Compatible with LP3470

- MAX6424/MAX6425 Pin Compatible with NCP300–NCP303, MC33464/MC33465, S807/S808/S809, and RN5VD

- MAX6426 Pin Compatible with PST92XX

Typical Operating Circuit, Selector Guide, and Ordering Information appear at end of data sheet.

# Low-Power, SC70/SOT µP Reset Circuits with Capacitor-Adjustable Reset Timeout Delay

### **Absolute Maximum Ratings**

| All voltages Referenced to GND |                           |

|--------------------------------|---------------------------|

| V <sub>CC</sub>                | 0.3V to +6.0V             |

| SRT, RESET, RESET (push-pull)  | 0.3V to $(V_{CC} + 0.3V)$ |

| RESET (open drain)             | 0.3V to +6.0V             |

| Input Current (all pins)       | ±20mA                     |

| Output Current (RESET, RESET)  | ±20mA                     |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |     |

|-------------------------------------------------------|-----|

| 4-Pin SC70 (derate 3.1mW/°C above +70°C)245n          | ηW  |

| 4-Pin SOT143 (derate 4mW/°C above +70°C)320n          | ηW  |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571n         | ηW  |

| Operating Temperature Range40°C to +125               | 5°C |

| Storage Temperature Range65°C to +150                 | 0°C |

| Junction Temperature+150                              | 0°C |

| Lead Temperature (soldering, 10s)+300                 | 0°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{CC} = 1V \text{ to } 5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified. Typical values are at } V_{CC} = 5V \text{ and } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                | SYMBOL               | CONDITIONS                                              | MIN                               | TYP                                         | MAX                    | UNITS |  |

|------------------------------------------|----------------------|---------------------------------------------------------|-----------------------------------|---------------------------------------------|------------------------|-------|--|

| Supply Voltage Range                     | V <sub>CC</sub>      |                                                         | 1.0                               |                                             | 5.5                    | V     |  |

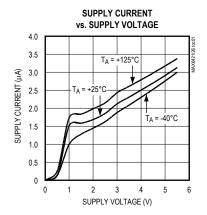

|                                          |                      | V <sub>CC</sub> ≤ 5.0V                                  |                                   | 2.5                                         | 4.2                    |       |  |

| Supply Current                           | Icc                  | V <sub>CC</sub> ≤ 3.3V                                  |                                   | 1.9                                         | 3.4                    | μA    |  |

|                                          |                      | VCC ≤ 2.0V                                              |                                   | 1.6                                         | 2.5                    | ]     |  |

| V Doost Throubold Assurage               | \/                   | T <sub>A</sub> = +25°C                                  | V <sub>TH</sub> - 1.5             | V <sub>TH</sub> - 1.5% V <sub>TH</sub> + 1. |                        | V     |  |

| V <sub>CC</sub> Reset Threshold Accuracy | V <sub>TH</sub>      | T <sub>A</sub> = -40°C to +125°C                        | V <sub>TH</sub> - 2.5             | 5% \                                        | √ <sub>TH</sub> + 2.5% | ]     |  |

| Hysteresis                               | V <sub>HYST</sub>    |                                                         |                                   | 4 x V <sub>Th</sub>                         | 1                      | mV    |  |

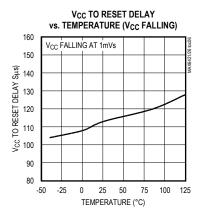

| V <sub>CC</sub> to Reset Delay           | t <sub>RD</sub>      | V <sub>CC</sub> falling at 1mV/μs                       |                                   | 80                                          |                        | μs    |  |

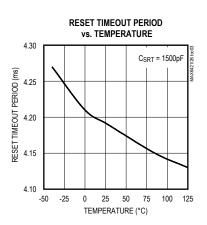

| Reset Timeout Period                     | +                    | C <sub>SRT</sub> = 1500pF                               | 3.00                              | 4.375                                       | 5.75                   | me    |  |

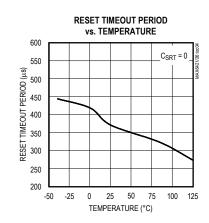

| Reset Timeout Period                     | t <sub>RP</sub>      | C <sub>SRT</sub> = 0                                    |                                   | 0.275                                       |                        | ms    |  |

| V <sub>SRT</sub> Ramp Current            | I <sub>RAMP</sub>    | $V_{SRT}$ = 0 to 0.65V; $V_{CC}$ = 1.6V to 5V           |                                   | 240                                         |                        | nA    |  |

| V <sub>SRT</sub> Ramp Threshold          | V <sub>TH-RAMP</sub> | V <sub>CC</sub> = 1.6V to 5V (V <sub>RAMP</sub> rising) |                                   | 0.65                                        |                        | V     |  |

| RAMP Threshold Hysteresis                |                      | V <sub>RAMP</sub> falling threshold                     |                                   | 33                                          |                        | mV    |  |

|                                          | V <sub>OL</sub>      | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> = 50μA        |                                   |                                             | 0.3                    |       |  |

| RESET Output Voltage Low                 |                      | V <sub>CC</sub> ≥ 2.7V, I <sub>SINK</sub> = 1.2mA       | 0.3                               |                                             | V                      |       |  |

|                                          |                      | V <sub>CC</sub> ≥ 4.5V, I <sub>SINK</sub> = 3.2mA       |                                   | 0.4                                         |                        |       |  |

| <del>DECET</del> 0 / 1 / 1 / 1 / 1 / 1   |                      | V <sub>CC</sub> ≥ 1.8V, I <sub>SOURCE</sub> = 200μA     | 0.8 x V <sub>C</sub>              | C                                           |                        |       |  |

| RESET Output Voltage High, Push-Pull     | V <sub>OH</sub>      | V <sub>CC</sub> ≥ 2.25V, I <sub>SOURCE</sub> = 500μA    | 0.8 x V <sub>C</sub>              | 0.8 x V <sub>CC</sub>                       |                        | ] v   |  |

| . don't dii                              |                      | V <sub>CC</sub> ≥ 4.5V, I <sub>SOURCE</sub> = 800μA     | 0.8 x V <sub>C</sub>              | C                                           |                        |       |  |

| RESET Output Leakage Current, Open-Drain | I <sub>LKG</sub>     | V <sub>CC</sub> > V <sub>TH</sub> , reset not asserted  |                                   |                                             | 1.0                    | μA    |  |

|                                          |                      | V <sub>CC</sub> ≥ 1.0V, I <sub>SOURCE</sub> = 1µA       | 0.8 x V <sub>C</sub>              |                                             |                        |       |  |

| DESET Output Voltage High                | V                    | V <sub>CC</sub> ≥ 1.8V, I <sub>SOURCE</sub> = 150μA     |                                   |                                             |                        | V     |  |

| RESET Output Voltage High                | V <sub>OH</sub>      | V <sub>CC</sub> ≥ 2.7V, I <sub>SOURCE</sub> = 500μA     |                                   |                                             |                        |       |  |

|                                          |                      | V <sub>CC</sub> ≥ 4.5V, I <sub>SOURCE</sub> = 800μA     | 4.5V, I <sub>SOURCE</sub> = 800μA |                                             |                        |       |  |

|                                          |                      | V <sub>CC</sub> ≥ 1.8V, I <sub>SINK</sub> = 500μA       |                                   |                                             | 0.3                    |       |  |

| RESET Output Voltage Low                 | V <sub>OL</sub>      | V <sub>CC</sub> ≥ 2.7V, I <sub>SINK</sub> = 1.2mA       | 0.3                               |                                             | V                      |       |  |

|                                          |                      | V <sub>CC</sub> ≥ 4.5V, I <sub>SINK</sub> = 3.2mA       |                                   |                                             | 0.4                    |       |  |

Note 1: Devices production tested at +25°C. Overtemperature limits are guaranteed by design.

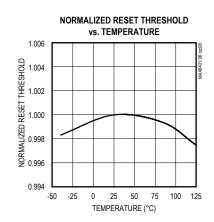

### **Typical Operating Characteristics**

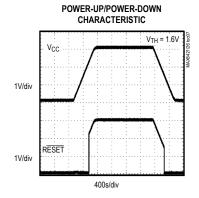

( $V_{CC}$  = 5V,  $C_{SRT}$  = 1500pF,  $T_A$  = +25°C, unless otherwise noted.)

#### **Pin Description**

|         | PIN                  |      |                    |         |                 |                                                                                                                                                                                                                                              |  |

|---------|----------------------|------|--------------------|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6340 | MAX6<br>MAX6<br>MAX6 | 422  | MAX6424<br>MAX6425 | MAX6426 | NAME            | FUNCTION                                                                                                                                                                                                                                     |  |

| SOT23   | SOT143               | SC70 | SOT23              | SOT23   |                 |                                                                                                                                                                                                                                              |  |

| 1       | 3                    | 3    | 5                  | 1       | SRT             | Set Reset Timeout Input. Connect a capacitor between SRT and ground to set the timeout period. Determine the period as follows: $t_{RP}$ = 2.73 × $10^6$ × $c_{SRT}$ + 275 $\mu$ s with $t_{RP}$ in seconds and $c_{SRT}$ in farads          |  |

| 2       | 1                    | 2    | 3                  | 2, 3    | GND             | Ground                                                                                                                                                                                                                                       |  |

| 3       | _                    | _    | 4                  | _       | N.C.            | Not Internally Connected. Can be connected to GND                                                                                                                                                                                            |  |

| 4       | 2                    | 1    | 2                  | 5       | V <sub>CC</sub> | Supply Voltage and Reset Threshold Monitor Input                                                                                                                                                                                             |  |

| 5       |                      |      | 1                  | 4       | RESET           | $\overline{\text{RESET}}$ changes from high to low whenever $\text{V}_{\text{CC}}$ drops below the selected reset threshold voltage. RESET remains low for the reset timeout period after $\text{V}_{\text{CC}}$ exceeds the reset threshold |  |

| _       | 4                    | 4    | _                  | _       | RESET           | RESET changes from low to high whenever $V_{CC}$ drops below the selected reset threshold voltage. RESET remains high for the reset timeout period after $V_{CC}$ exceeds the reset threshold                                                |  |

#### **Detailed Description**

#### **Reset Output**

The reset output is typically connected to the reset input of a  $\mu P$ . A  $\mu P$ 's reset input starts or restarts the  $\mu P$  in a known state. The MAX6340/MAX6421–MAX6426  $\mu P$  supervisory circuits provide the reset logic to prevent code-execution errors during power-up, power-down, and brownout conditions (see *Typical Operating Characteristics*).

$\overline{\text{RESET}}$  changes from high to low whenever V<sub>CC</sub> drops below the threshold voltage. Once V<sub>CC</sub> exceeds the threshold voltage,  $\overline{\text{RESET}}$  remains low for the capacitor-adjustable reset timeout period.

The MAX6422 active-high RESET output is the inverse logic of the active-low  $\overline{\text{RESET}}$  output. All device outputs are guaranteed valid for  $V_{CC} > 1V$ .

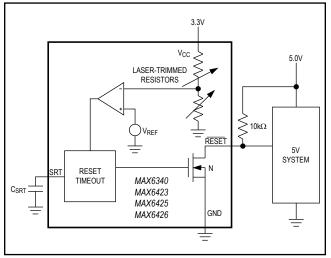

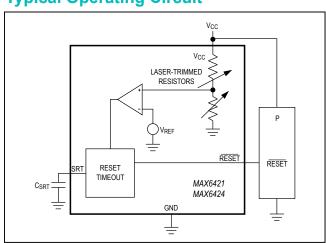

The MAX6340/MAX6423/MAX6425/MAX6426 are opendrain  $\overline{RESET}$  outputs. Connect an external pullup resistor to any supply from 0 to 5.5V. Select a resistor value large enough to register a logic low when  $\overline{RESET}$  is asserted and small enough to register a logic high while supplying all input current and leakage paths connected to the  $\overline{RESET}$  line. A  $10k\Omega$  to  $100k\Omega$  pullup is sufficient in most applications.

Figure 1. MAX6340/MAX6423/MAX6425/MAX6426 Open-Drain RESET Output Allows Use with Multiple Supplies

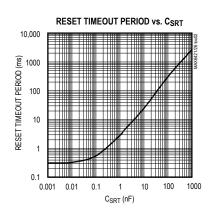

#### **Selecting a Reset Capacitor**

The reset timeout period is adjustable to accommodate a variety of  $\mu P$  applications. Adjust the reset timeout period ( $t_{RP}$ ) by connecting a capacitor ( $C_{SRT}$ ) between SRT and ground. Calculate the reset timeout capacitor as follows:

# Low-Power, SC70/SOT µP Reset Circuits with Capacitor-Adjustable Reset Timeout Delay

$C_{SRT} = (t_{RP} - 275\mu s) / (2.73 5 10^6)$

where t<sub>RP</sub> is in seconds and C<sub>SRT</sub> is in farads.

The reset delay time is set by a current/capacitor-controlled ramp compared to an internal 0.65V reference. An internal 240nA ramp current source charges the external capacitor. The charge to the capacitor is cleared when a reset condition is detected. Once the reset condition is removed, the voltage on the capacitor ramps according to the formula: dV/dt = I/C. The  $C_{SRT}$  capacitor must ramp to 0.65V to deassert the reset.  $C_{SRT}$  must be a low-leakage (<10nA) type capacitor; ceramic is recommended.

#### **Operating as a Voltage Detector**

The MAX6340/MAX6421–MAX6426 can be operated in a voltage detector mode by floating the SRT pin. The reset delay times for  $V_{CC}$  rising above or falling below the threshold are not significantly different. The reset output is deasserted smoothly without false pulses.

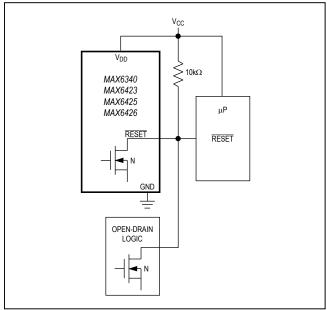

Figure 2. Wired-OR Reset Circuit

#### **Applications Information**

# Interfacing to Other Voltages for Logic Compatibility

The open-drain outputs of the MAX6340/MAX6423/ MAX6425/MAX6426 can be used to interface to  $\mu$ Ps with other logic levels. As shown in Figure 1, the open-drain output can be connected to voltages from 0 to 5.5V. This allows for easy logic compatibility to various  $\mu$ Ps.

#### Wired-OR Reset

To allow auxiliary circuitry to hold the system in reset, an external open-drain logic signal can be connected to the open-drain RESET of the MAX6340/MAX6423/MAX6425/MAX6426, as shown in Figure 2. This configuration can reset the  $\mu P$ , but does not provide the reset timeout when the external logic signal is released.

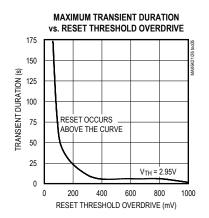

#### **Negative-Going Vcc Transients**

In addition to issuing a reset to the  $\mu P$  during power-up, power-down, and brownout conditions, these supervisors are relatively immune to short-duration negative-going transients (glitches). The graph Maximum Transient Duration vs. Reset Threshold Overdrive in the *Typical Operating Characteristics* shows this relationship.

The area below the curve of the graph is the region in which these devices typically do not generate a reset pulse. This graph was generated using a negative-going pulse applied to  $V_{CC},\,$  starting above the actual reset threshold ( $V_{TH}$ ) and ending below it by the magnitude indicated (reset-threshold overdrive). As the magnitude of the transient decreases (farther below the reset threshold), the maximum allowable pulse width decreases. Typically, a  $V_{CC}$  transient that goes 100mV below the reset threshold and lasts 50 $\mu$ s or less does not cause a reset pulse to be issued.

#### Ensuring a Valid RESET or $\overline{RESET}$ Down to $V_{CC} = 0$

When  $V_{CC}$  falls below 1V,  $\overline{RESET}/RESET$  current-sinking (sourcing) capabilities decline drastically. In the case of the MAX6421/MAX6424, high-impedance CMOS-logic inputs connected to  $\overline{RESET}$  can drift to undetermined voltages. This presents no problems in most applications, since most  $\mu Ps$  and other circuitry do not operate with  $V_{CC}$  below 1V.

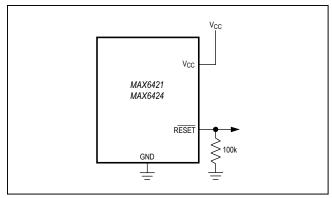

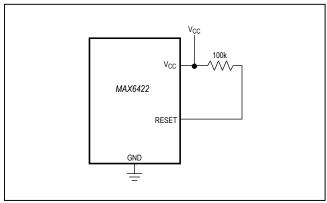

In those applications where  $\overline{\text{RESET}}$  must be valid down to zero, adding a pulldown resistor between  $\overline{\text{RESET}}$  and ground sinks any stray leakage currents, holding  $\overline{\text{RESET}}$  low (Figure 3). The value of the pulldown resistor is not critical;  $100 \text{k}\Omega$  is large enough not to load  $\overline{\text{RESET}}$  and small enough to pull  $\overline{\text{RESET}}$  to ground. For applications using the MAX6422, a  $100 \text{k}\Omega$  pullup resistance.

Figure 3. Ensuring  $\overline{RESET}$  Valid to  $V_{CC} = 0$

Figure 4. Ensuring RESET Valid to  $V_{CC} = 0$

tor between RESET and VCC holds RESET high when VCC falls below 1V (Figure 4). Open-drain RESET versions are not recommended for applications requiring valid logic for  $V_{CC}$  down to zero.

#### **Layout Consideration**

SRT is a precise current source. When developing the layout for the application, be careful to minimize board capacitance and leakage currents around this pin. Traces connected to SRT should be kept as short as possible. Traces carrying high-speed digital signals and traces with large voltage potentials should be routed as far from SRT as possible. Leakage current and stray capacitance (e.g., a scope probe) at this pin could cause errors in the reset timeout period. When evaluating these parts, use clean prototype boards to ensure accurate reset periods.

**Table 1. Reset Threshold Voltage Suffix**

| SUFFIX | MIN   | TYP   | MAX   |

|--------|-------|-------|-------|

| 16     | 1.536 | 1.575 | 1.614 |

| 17     | 1.623 | 1.665 | 1.707 |

| 18     | 1.755 | 1.800 | 1.845 |

| 19     | 1.853 | 1.900 | 1.948 |

| 20     | 1.950 | 2.000 | 2.050 |

| 21     | 2.048 | 2.100 | 2.153 |

| 22     | 2.133 | 2.188 | 2.243 |

| 23     | 2.313 | 2.313 | 2.371 |

| 24     | 2.340 | 2.400 | 2.460 |

| 25     | 2.438 | 2.500 | 2.563 |

| 26     | 2.559 | 2.625 | 2.691 |

| 27     | 2.633 | 2.700 | 2.768 |

| 28     | 2.730 | 2.800 | 2.870 |

| 29     | 2.852 | 2.925 | 2.998 |

| 30     | 2.925 | 3.000 | 3.075 |

| 31     | 2.998 | 3.075 | 3.152 |

| 32     | 3.120 | 3.200 | 3.280 |

| 33     | 3.218 | 3.300 | 3.383 |

| 34     | 3.315 | 3.400 | 3.485 |

| 35     | 3.413 | 3.500 | 3.558 |

| 36     | 3.510 | 3.600 | 3.690 |

| 37     | 3.608 | 3.700 | 3.793 |

| 38     | 3.705 | 3.800 | 3.895 |

| 39     | 3.803 | 3.900 | 3.998 |

| 40     | 3.900 | 4.000 | 4.100 |

| 41     | 3.998 | 4.100 | 4.203 |

| 42     | 4.095 | 4.200 | 4.305 |

| 43     | 4.193 | 4.300 | 4.408 |

| 44     | 4.266 | 4.375 | 4.484 |

| 45     | 4.388 | 4.500 | 4.613 |

| 46     | 4.509 | 4.625 | 4.741 |

| 47     | 4.583 | 4.700 | 4.818 |

| 48     | 4.680 | 4.800 | 4.920 |

| 49     | 4.778 | 4.900 | 5.023 |

| 50     | 4.875 | 5.000 | 5.125 |

#### **Standard Versions Table**

| Otalidara Versions | Table            |

|--------------------|------------------|

| PART*              | OUTPUT STAGE     |

| MAX6340UK16+T      | Open-Drain RESET |

| MAX6340UK22+T      | Open-Drain RESET |

| MAX6340UK26+T      | Open-Drain RESET |

| MAX6340UK29+T      | Open-Drain RESET |

| MAX6340UK46+T      | Open-Drain RESET |

| MAX6421US16+T      | Push-Pull RESET  |

| MAX6421XS16+T      | Push-Pull RESET  |

| MAX6421US22+T      | Push-Pull RESET  |

| MAX6421XS22+T      | Push-Pull RESET  |

| MAX6421US26+T      | Push-Pull RESET  |

| MAX6421XS26+T      | Push-Pull RESET  |

| MAX6421US29+T      | Push-Pull RESET  |

| MAX6421XS29+T      | Push-Pull RESET  |

| MAX6421US46+T      | Push-Pull RESET  |

| MAX6421XS46+T      | Push-Pull RESET  |

| MAX6422US16+T      | Push-Pull RESET  |

| MAX6422XS16+T      | Push-Pull RESET  |

| MAX6422US22+T      | Push-Pull RESET  |

| MAX6422XS22+T      | Push-Pull RESET  |

| MAX6422US26+T      | Push-Pull RESET  |

| MAX6422XS26+T      | Push-Pull RESET  |

| MAX6422US29+T      | Push-Pull RESET  |

| MAX6422XS29+T      | Push-Pull RESET  |

| MAX6422US46+T      | Push-Pull RESET  |

| MAX6422XS46+T      | Push-Pull RESET  |

|                    |                  |

## **Typical Operating Circuit**

| PART*         | OUTPUT STAGE     |

|---------------|------------------|

| MAX6423US16+T | Open-Drain RESET |

| MAX6423XS16+T | Open-Drain RESET |

| MAX6423US22+T | Open-Drain RESET |

| MAX6423XS22+T | Open-Drain RESET |

| MAX6423US26+T | Open-Drain RESET |

| MAX6423XS26+T | Open-Drain RESET |

| MAX6423US29+T | Open-Drain RESET |

| MAX6423XS29+T | Open-Drain RESET |

| MAX6423US46+T | Open-Drain RESET |

| MAX6423XS46+T | Open-Drain RESET |

| MAX6424UK16+T | Push-Pull RESET  |

| MAX6424UK22+T | Push-Pull RESET  |

| MAX6424UK26+T | Push-Pull RESET  |

| MAX6424UK29+T | Push-Pull RESET  |

| MAX6424UK46+T | Push-Pull RESET  |

| MAX6425UK16+T | Open-Drain RESET |

| MAX6425UK22+T | Open-Drain RESET |

| MAX6425UK26+T | Open-Drain RESET |

| MAX6425UK29+T | Open-Drain RESET |

| MAX6425UK46+T | Open-Drain RESET |

| MAX6426UK16+T | Open-Drain RESET |

| MAX6426UK22+T | Open-Drain RESET |

| MAX6426UK26+T | Open-Drain RESET |

| MAX6426UK29+T | Open-Drain RESET |

| MAX6426UK46+T | Open-Drain RESET |

<sup>\*</sup>Sample stock is generally held on all standard versions. Contact factory for availability of nonstandard versions.

## **Pin Configurations (continued)**

### **Selector Guide**

| PART    | PUSH-PULL RESET | PUSH-PULL RESET | OPEN-DRAIN RESET | PIN-PACKAGE   |

|---------|-----------------|-----------------|------------------|---------------|

| MAX6340 | _               | _               | V                | 5 SOT23       |

| MAX6421 | V               | _               | _                | 4 SOT143/SC70 |

| MAX6422 | <del>_</del>    | <b>✓</b>        | _                | 4 SOT143/SC70 |

| MAX6423 | _               | _               | V                | 4 SOT143/SC70 |

| MAX6424 | <b>V</b>        | _               | _                | 5 SOT23       |

| MAX6425 | <del>_</del>    | _               | V                | 5 SOT23       |

| MAX6426 | _               | _               | V                | 5 SOT23       |

# Low-Power, SC70/SOT µP Reset Circuits with Capacitor-Adjustable Reset Timeout Delay

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX6340UK+T   | -40°C to +125°C | 5 SOT23-5   |

| MAX6340UK/V+T | -40°C to +125°C | 5 SOT23-5   |

| MAX6421XS+T   | -40°C to +125°C | 4 SC70-4    |

| MAX6421US+T   | -40°C to +125°C | 4 SOT143-4  |

| MAX6421UST    | -40°C to +125°C | 4 SOT143-4  |

| MAX6422XS+T   | -40°C to +125°C | 4 SC70-4    |

| MAX6422US+T   | -40°C to +125°C | 4 SOT143-4  |

| MAX6422UST    | -40°C to +125°C | 4 SOT143-4  |

| MAX6423XS+T   | -40°C to +125°C | 4 SC70-4    |

| MAX6423US+T   | -40°C to +125°C | 4 SOT143-4  |

| MAX6423UST    | -40°C to +125°C | 4 SOT143-4  |

| MAX6424UK+T   | -40°C to +125°C | 5 SOT23-5   |

| MAX6424UKT    | -40°C to +125°C | 5 SOT23-5   |

| MAX6425UK+T   | -40°C to +125°C | 5 SOT23-5   |

| MAX6425UKT    | -40°C to +125°C | 5 SOT23-5   |

| MAX6426UK+T   | -40°C to +125°C | 5 SOT23-5   |

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 4 SC70          | X4+1            | 21-0098        | 90-0187             |

| 4 SOT143        | U4+1            | 21-0052        | 90-0183             |

| 5 SOT23         | U5+2            | 21-0057        | 90-0174             |

# Low-Power, SC70/SOT µP Reset Circuits with Capacitor-Adjustable Reset Timeout Delay

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                            | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 5                  | 3/14             | Added /V OPN to Ordering Information                                                                                                   | 1                |

| 6                  | 12/15            | Added lead-free part numbers to <i>Ordering Information</i> table and removed top mark information from <i>Standard Versions</i> table | 1, 8             |

| 7                  | 1/16             | Changed MAX6340UK/V-T to MAX6340UK/V+T in Ordering Information table                                                                   | 9                |