# SGM61012/SGM61022 1.2A/2A High-Efficiency Buck Converters with AHP-COT Mode

## **GENERAL DESCRIPTION**

The SGM61012 and SGM61022 are efficient high frequency synchronous Buck converters with an input voltage range of 2.3V to 5.5V and a wide output current range that is optimized for compact solutions. It operates in PWM mode at heavy loads and automatically enters power-save mode (PSM) at light loads to maintain its high efficiency.

Setting the MODE pin can enable deep sleep mode. This device operates with an ultra-low quiescent current, and it can maintain high efficiency at very low load. This function keeps the standby current at its lowest level, and can increase the standby time of battery-powered application. To meet the requirements of system power rails, the output capacitors with values above  $100\mu F$  can be used by the internal loop compensation.

With its adaptive hysteresis and pseudo-constant on-time control (AHP-COT) architecture, the load transient performance is excellent and the output voltage regulation accuracy is achieved.

The SGM61012 and SGM61022 are available in a Green TDFN-2×2-8AL package.

## **FEATURES**

- Input Voltage Range: 2.3V to 5.5V

- AHP-COT Architecture

- Output Current: SGM61012: 1.2A SGM61022: 2A

- 9µA Ultra-Low Quiescent Current in Deep Sleep Mode

- Fast Transient Regulation

- 100% Duty Cycle Capability

- High-Efficiency Deep Sleep Mode under Light Load

- Output Discharge

- Short-Circuit Protection

- Power Good Output

- Thermal Shutdown

- Available in a Green TDFN-2×2-8AL Package

## **APPLICATIONS**

General Purpose Point-of-Load Power Supplies Battery-Powered Applications

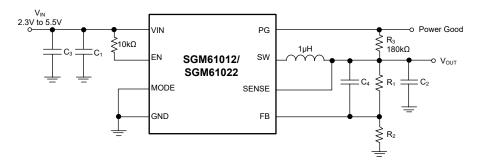

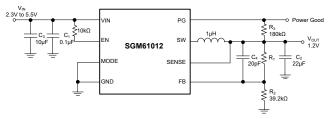

## TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

## PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM61012 | TDFN-2×2-8AL           | -40°C to +125°C                   | SGM61012XTDE8G/TR  | GKG<br>XXXX        | Tape and Reel, 3000 |

| SGM61022 | TDFN-2×2-8AL           | -40°C to +125°C                   | SGM61022XTDE8G/TR  | GJZ<br>XXXX        | Tape and Reel, 3000 |

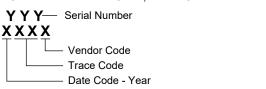

## MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| VIN, PG and SENSE Voltages        | 0.3V to 6V                     |

|-----------------------------------|--------------------------------|

| SW Voltage                        | TBDV to TBDV                   |

| FB Voltage                        | 0.3V to 3.6V                   |

| EN and MODE Voltages              | 0.3V to V <sub>IN</sub> + 0.3V |

| Sink Current at PG                | 0mA to 0.5mA                   |

| Package Thermal Resistance        |                                |

| TDFN-2×2-8AL, θ <sub>JA</sub>     | TBD°C/W                        |

| Junction Temperature              | +150°C                         |

| Storage Temperature Range         | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s) | +260°C                         |

| ESD Susceptibility                |                                |

| HBM                               | 4000V                          |

## RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range                 | 2.3V to 5.5V   |

|-------------------------------------|----------------|

| Output Voltage Range                | 0.5V to 4V     |

| Operating Ambient Temperature Range | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

## **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

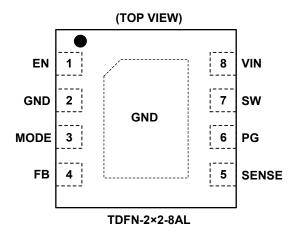

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN         | NAME  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                 |

|-------------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | EN    | I                  | Logic high sets the device active, logic low disables it and turns it into shutdown mode. It can connect a $10k\Omega$ resistor to VIN pin if it is needed. Do not leave this pin floating. |

| 2           | GND   | G                  | Power and Signal Ground.                                                                                                                                                                    |

| 3           | MODE  | I                  | Enable Setting for Deep Sleep Mode. The device adaptively goes into deep sleep mode when logic high, and does not enter it when logic low. Do not leave this pin floating.                  |

| 4           | FB    | 1                  | Feedback Input. An external feedback divider is needed for setting the output voltage.                                                                                                      |

| 5           | SENSE | I                  | Output Voltage Sense Pin. Must be connected to output voltage.                                                                                                                              |

| 6           | PG    | 0                  | Power Good Open-Drain Output. If the output voltage is less than the regulation limit, this pin is pulled low. Leave this pin floating when not in use.                                     |

| 7           | SW    | Р                  | Switching Node.                                                                                                                                                                             |

| 8           | VIN   | Р                  | Power Supply Voltage Input.                                                                                                                                                                 |

| Exposed Pad | GND   | _                  | Connect it to GND. The thermal pad must be soldered to improve heat dissipation.                                                                                                            |

NOTE: 1. I = input, O = output, P = power, G = ground.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, T_J = +25^{\circ}C, MODE = Low, unless otherwise noted.)$

| PARAMETER                                    | SYMBOL              | CONDITIONS                                                                      | MIN | TYP  | MAX | UNITS |

|----------------------------------------------|---------------------|---------------------------------------------------------------------------------|-----|------|-----|-------|

| Supply                                       |                     |                                                                                 | •   |      |     | •     |

| Input Voltage Range                          | $V_{IN}$            |                                                                                 | 2.3 |      | 5.5 | V     |

| Quiescent Current into VIN                   |                     | I <sub>OUT</sub> = 0mA, device no switching                                     |     | 25   |     | μΑ    |

| Quiescent Current into VIN (Deep Sleep Mode) | lα                  | I <sub>OUT</sub> = 0mA, device no switching, MODE = High                        |     | 9    |     | μΑ    |

| Shutdown Current into VIN                    | I <sub>SD</sub>     | EN = Low                                                                        |     |      | TBD | μΑ    |

| Under-Voltage Lockout                        | \/                  | Input voltage falling                                                           |     | 1.8  |     | V     |

| Under-Voltage Lockout Hysteresis             | $V_{\text{UVLO}}$   | Rising above V <sub>UVLO</sub>                                                  |     | 120  |     | mV    |

| Thermal Shutdown                             | _                   | Temperature rising                                                              |     | +160 |     | °C    |

| Thermal Shutdown Hysteresis                  | $T_{JSD}$           | Temperature falling below T <sub>JSD</sub>                                      |     | +25  |     | °C    |

| Logic Interface (EN Mode)                    |                     |                                                                                 |     |      |     |       |

| High Level Input Voltage                     | V <sub>IH</sub>     | V <sub>IN</sub> = 2.3V to 5.5V                                                  | 1   |      |     | V     |

| Low Level Input Voltage                      | V <sub>IL</sub>     | V <sub>IN</sub> = 2.3V to 5.5V                                                  |     |      | 0.4 | V     |

| Input Leakage Current                        | $I_{LKG}$           |                                                                                 |     | 0.01 | TBD | μΑ    |

| Power Good                                   |                     |                                                                                 |     |      |     |       |

| Power Good Threshold                         | .,                  | V <sub>OUT</sub> falling referenced to V <sub>OUT</sub> nominal                 |     | -10  |     | %     |

| Power Good Hysteresis                        | $V_{PG}$            |                                                                                 |     | 5    |     | %     |

| Low Level Voltage                            | V <sub>OL</sub>     | I <sub>SINK</sub> = 500μA                                                       |     |      | TBD | V     |

| PG Leakage Current                           | I <sub>PG,LKG</sub> | V <sub>PG</sub> = 5.0V                                                          |     | 0.01 | TBD | μΑ    |

| Output                                       |                     |                                                                                 |     |      |     |       |

| Output Voltage Range                         |                     |                                                                                 | 0.5 |      | 4.0 | V     |

| Deep Sleep Mode Output Voltage<br>Accuracy   | V <sub>OUT</sub>    | MODE = High; V <sub>IN</sub> ≥ 2.3V and V <sub>IN</sub> ≥ V <sub>OUT</sub> + 1V | TBD |      | TBD | %     |

| Feedback Regulation Voltage                  | $V_{FB}$            | $V_{IN} \ge 2.3V$ and $V_{IN} \ge V_{OUT} + 1V$                                 |     | 0.45 |     | V     |

| Feedback Input Bias Current                  | I <sub>FB</sub>     | V <sub>FB</sub> = 0.45V                                                         |     | 1    | TBD | nA    |

| Output Discharge Resistor                    | R <sub>DIS</sub>    | EN = Low, V <sub>OUT</sub> = 1.8V                                               |     | 0.9  |     | kΩ    |

| Line Regulation                              |                     |                                                                                 |     | TBD  |     | %/V   |

| High-side MOSFET On-Resistance               | В                   | I <sub>SW</sub> = 500mA                                                         |     | 119  |     | mΩ    |

| Low-side MOSFET On-Resistance                | $R_{DS(ON)}$        | I <sub>SW</sub> = 500mA                                                         |     | 80   |     | mΩ    |

| High-side MOSFET Switch Current              |                     | Rising inductor current (SGM61012)                                              |     | 2.8  |     | Α     |

| Limit                                        | I <sub>LIM</sub>    | Rising inductor current (SGM61022)                                              |     | 3.5  |     | Α     |

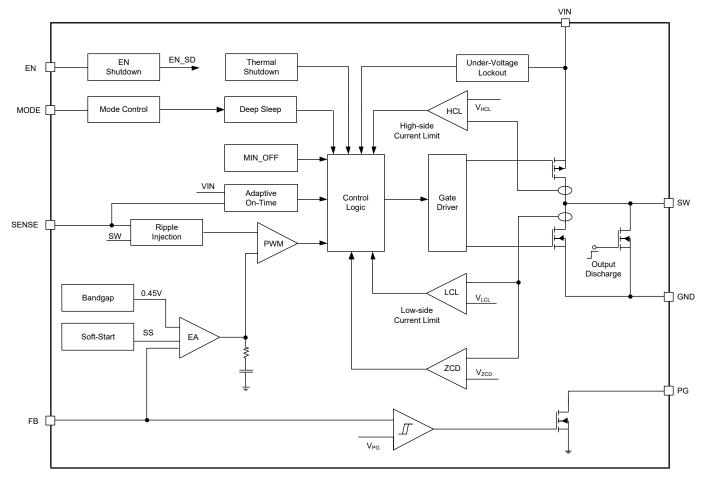

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

## **DETAILED DESCRIPTION**

#### Overview

The SGM61012 and SGM61022 are high-efficient Buck converters with AHP-COT architecture and advanced regulation topology.

At medium to heavy loads, the device works in pulse width modulation (PWM) mode. At light load, it automatically switches to power-save mode (PSM). In PWM mode, the device works with a nominal switching frequency of 2MHz. When the load current falls, the device goes into PSM to achieve high efficiency with reducing switching frequency and minimizing quiescent current.

When pulling up the MODE pin, the device can enter deep sleep mode automatically at very light load to achieve high efficiency. If the circuit has no load current,  $9\mu A$  low quiescent current is sufficient to maintain the output voltage. Deep sleep mode can reduce the standby energy consumption of system. During shutdown mode, the energy consumption falls below  $1\mu A$ .

## **Under-Voltage Lockout (UVLO)**

The device implements the under-voltage lockout (UVLO) with a 120mV (TYP) hysteresis. When the input voltage falls below the  $V_{\text{UVLO}}$ , it shuts down the device.

#### **Enable and Disable**

A logic high input to EN activates the device, and a logic low disables the device. A  $10k\Omega$  resistor is recommended to add between EN and VIN, and do not leave it floating.

## Power Good (PG)

The power good output of SGM61012 and SGM61022 will be low in the condition that the output voltage less than its nominal value. If the output exceeds 95% of the regulated voltage, the power good is in high impedance state. If the output voltage is less than 90% of the regulated voltage, the power good is driven to low.

The PG pin is an open-drain output with a maximum of 0.5mA sink current. A pull-up resistor connecting to

power good output is required. When the device is disabled or under-voltage lockout, the PG pin is driven to low (see Table 1). The PG signal connected to the EN pin of other converters can be used for multiple rails sequences. Leave the PG pin floating when not in use.

Table 1. Logic Table of PG Pin

| Dovice                  | Information                | Logic Status |     |  |  |

|-------------------------|----------------------------|--------------|-----|--|--|

| Device                  | IIIIoiiiiatioii            | High Z       | Low |  |  |

| Enable                  | $V_{FB} \ge V_{PG}$        | √            |     |  |  |

| (EN = High)             | $V_{FB} \le V_{PG}$        |              | √   |  |  |

| Shutdown<br>(EN = Low)  |                            | <b>V</b>     |     |  |  |

| UVLO                    | $0.7V < V_{IN} < V_{UVLO}$ | $\checkmark$ |     |  |  |

| Thermal<br>Shutdown     | $T_J > T_{JSD}$            | √            |     |  |  |

| Power Supply<br>Removal | V <sub>IN</sub> < 0.7V     | V            |     |  |  |

## 100% Duty Cycle

The device provides low input-to-output voltage drop by going into 100% duty cycle mode. In this mode, the high-side MOSFET is constantly turned on and the low-side MOSFET is turned off. This function can increase the operation time to the utmost extent for battery powered applications. To maintain an appropriate output voltage, the minimum input voltage is calculated by:

$$V_{\text{IN MIN}} = V_{\text{OUT}} + I_{\text{OUT MAX}} \times (R_{\text{DSON}} + R_{\text{L}})$$

(1)

where:

- V<sub>IN MIN</sub> is the minimum input voltage.

- I<sub>OUT MAX</sub> is the maximum output current.

- R<sub>DSON</sub> is the high-side MOSFET on-resistance.

- R<sub>L</sub> is the inductor ohmic resistance.

## **Output Discharge**

Whenever the device is disabled by enable, thermal shutdown or under-voltage lockout, the output is discharged by the SW pin through a typical discharge resistor of  $R_{\text{DIS}}$ .

# **DETAILED DESCRIPTION (continued)**

#### **Soft-Start**

When EN is set to logic high and after about 150 $\mu$ s delay, the device starts switching and  $V_{OUT}$  increases with 600 $\mu$ s (TYP) internal soft-start circuit.

#### **Inductor Current Limit**

The device implements an inductor current limit if there is over-current or short-circuit. Both the peak current of high-side and valley current of low-side power MOSFETs are limited to protect the device. The high-side MOSFET is turned off and the low-side MOSFET is turned on to reduce the inductor current when the high-side switch current limit is triggered. The low-side MOSFET is turned off and the high-side switch is turned on again when the inductor current drops to the low-side switch current limit. It repeats until the inductor current falls below the high-side switch current limit. The actual current limit value may larger than the static current limit due to internal propagation delays.

## **Power-Save Mode (PSM)**

Once the load current decreases, setting MODE pin low, the SGM61012 and SGM61022 will enter power-save mode. Then, the device has a reduced switching frequency and works with the minimum quiescent current to keep high efficiency. In power-save mode, the inductor current is discontinuous. Then a fixed on-time architecture is activated and the typical on-time is  $t_{\text{ON}} = 500 \text{ns} \times (V_{\text{OUT}}/V_{\text{IN}})$ .

## **Deep Sleep Mode**

The SGM61012 and SGM61022 provide a deep sleep mode function, which is enabled by setting MODE pin high. The device enters into this mode when load current decreases to about 6.5mA  $^{(1)}$ , and exits when load current is greater than 15mA  $^{(1)}$ . Once enters deep sleep mode, all other control blocks are shut down, and only a dedicated low power consuming block monitors the output voltage. In this mode, the quiescent current consumption of the device is about 9 $\mu$ A (TYP), and the output voltage is 2% higher than the setting voltage approximately.

Even in the deep sleep mode, the dynamic load regulation of SGM61012 or SGM61022 is excellent.

NOTE: 1. Test condition:  $V_{IN} = 3.6V$ ,  $V_{OUT} = 1.8V$ ,  $L = 1\mu H$ .

#### **Thermal Shutdown**

To protect the device from overheating damage, thermal protection is included in the device. If the junction temperature exceeds the typical  $T_{JSD}$  (+160°C TYP), the switching will stop. When the device temperature drops below the threshold minus hysteresis, the switching will resume automatically.

## APPLICATION INFORMATION

The SGM61012 and SGM61022 are synchronous Buck converters with output voltage adjusted by feedback dividers. Taking SGM61012 typical application as a reference, the following sections discuss the design of external components and how to achieve the application.

Figure 3. SGM61012 Typical Application Circuit

## Requirements

The design parameters given in Table 2 are used for this design example.

**Table 2. Design Parameters**

| Design Parameter      | Example Value |

|-----------------------|---------------|

| Input Voltage         | 2.3V to 5.5V  |

| Output Voltage        | 1.2V          |

| Output Ripple Voltage | < 20mV        |

| Output Current (MAX)  | 1.2A          |

## **Design Details**

Table 3 shows the components included in this example.

**Table 3. Components List**

| Reference      | Description                                                                | Manufacturer |

|----------------|----------------------------------------------------------------------------|--------------|

| L <sub>1</sub> | 1μH, Power Inductor,<br>SGM61012 3A or SGM61022 4.5A                       | Std          |

| C <sub>1</sub> | 0.1µF, Ceramic Capacitor, 10V,<br>X7R, Size 0603                           | Std          |

| C <sub>2</sub> | 22μF, Ceramic Capacitor, 6.3V,<br>X7R, Size 0805                           | Std          |

| C <sub>3</sub> | 10μF, Ceramic Capacitor, 10V, X7R,<br>Size 0805                            | Std          |

| C <sub>4</sub> | 20pF, Ceramic Capacitor, 50V, C0G,<br>Size 0603                            | Std          |

| R <sub>1</sub> | Depending on the output voltage,<br>Chip Resistor, 1/16W, 1%,<br>Size 0603 | Std          |

| R <sub>2</sub> | 39.2kΩ, Chip Resistor, 1/16W, 1%,<br>Size 0603                             | Std          |

| R <sub>3</sub> | 180kΩ, Chip Resistor, 1/16W, 1%, Size 0603                                 | Std          |

## **Adjustable Output Voltage**

An external resistor divider connected to FB pin is used for setting the output voltage. Through adjusting  $R_1$  and  $R_2$ , the output voltage can be programmed to the desired value. Calculate  $R_1$  and  $R_2$  with Equation 2.

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right) = 0.45V \times \left(1 + \frac{R_1}{R_2}\right)$$

(2)

$R_2$  should be less than  $40k\Omega$  for higher accuracy. Make sure that the current flowing through  $R_2$  is at least 100 times greater than the current of FB pin. A lower value of  $R_2$  increases the robustness against noise injection, and higher values reduce the input current.

A feed-forward capacitor is recommended to improve the performance of smooth transition into power-save mode and reduce undershoot during load transient. 10 to 20pF is enough for typical applications.

## **Output Filter**

The output low pass filter is the combination of inductor and output capacitor. Table 4 shows the suggested value.

**Table 4. Inductor and Capacitor Combinations**

| L (µH) <sup>(1)</sup> | С <sub>оит</sub> (µF) <sup>(2)</sup> |           |    |  |  |  |

|-----------------------|--------------------------------------|-----------|----|--|--|--|

| L (μπ)                | 10                                   | 22        | 47 |  |  |  |

| 0.47                  |                                      | √         | √  |  |  |  |

| 1                     | √                                    | √ (3) (4) | √  |  |  |  |

| 2.2                   | √                                    | √         |    |  |  |  |

#### NOTES:

- 1. Expected inductor tolerance and current de-rating. Effective inductance has +20% and -30% variation.

- 2. Expected capacitance tolerance and bias voltage de-rating. Effective capacitance has +20% and -50% variation.

- 3. " $\sqrt{\ }$ " means the recommended filter combinations.

- 4. Filter combination in typical application.

# **APPLICATION INFORMATION (continued)**

## **Inductor Design**

Equation 3 is conventionally used to calculate the output inductance of a Buck converter. The inductor should be selected by its value and the saturation current. The saturation current of inductor should be higher than  $I_{L\_MAX}$  in Equation 3, and sufficient margin should be reserved. Typically, the current above high-side current limit is enough, and a 10% to 30% ripple current is selected to calculate the inductance. Larger inductor can reduce the ripple current, but with an increasing response time.

$$I_{L\_MAX} = I_{OUT\_MAX} + \frac{\Delta I_{L}}{2}$$

$$\Delta I_{L} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f_{OUT}}$$

(3)

#### where:

- I<sub>OUT MAX</sub> is the maximum output current.

- $\Delta I_L$  is the inductor current ripple.

- f<sub>SW</sub> is the switching frequency.

- L is the inductor value.

## **Capacitor Design**

For input capacitor design, a X5R/X7R dielectric ceramic capacitor should be selected for its low ESR and high frequency performance. 10µF is enough for most applications. The voltage rating of input capacitor must be considered for its significant bias effect. The input ripple voltage can be calculated from Equation 4.

$$\Delta V_{\text{IN}} = \frac{I_{\text{OUT}} \times D \times (1 - D)}{C_{\text{IN}} \times f_{\text{eve}}} \tag{4}$$

The ripple current rating of input capacitor should be greater than I<sub>CIN\_RMS</sub> in Equation 5 and the maximum value occurs at 50% duty cycle. A 0.1µF capacitor is suggested to add for further input decoupling of device.

$$I_{\text{CIN\_RMS}} = I_{\text{OUT}} \times \sqrt{\frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times V_{\text{IN}}}} = I_{\text{OUT}} \times \sqrt{D \times (1 - D)}$$

(5)

For output capacitor design, output ripple, transient response and loop stability should be considered. Minimum capacitance of output ripple criteria can be calculated from Equation 6.

$$C_{OUT} > \frac{\Delta I_L}{8 \times f_{SW} \times V_{OUT} \text{ RIPPLE}}$$

(6)

Both the input and output capacitors should be placed as close to VIN/Sense and GND pins as possible to reduce noise caused by PCB parasitic parameters.

To simplify customer's design process, the inductor and output capacitor combinations are recommended in Table 4.

## **Layout Considerations**

Good PCB layout is the key factor for high performance operation of a device regarding the stability, regulation, efficiency and other performance measures.

A list of guidelines for designing the PCB layout of SGM61012/SGM61022 is provided below:

Place the power components close together and connect them with short and wide routes. The

- low-side of the capacitors must be connected to GND properly to avoid potential shift.

- Signal traces are connected to the FB and SENSE pins. Connect the inductor with a short trace. Keep the traces away from SW nodes.

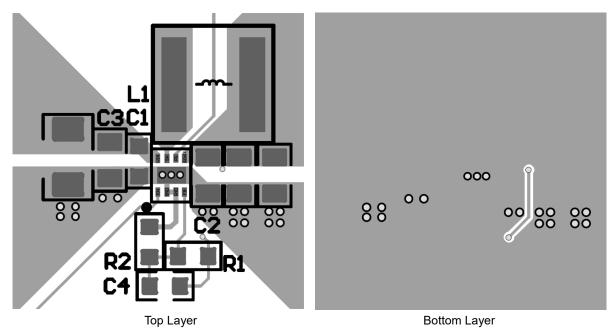

- Typical suggested layout is provided in Figure 4.

Figure 4. PCB Layout

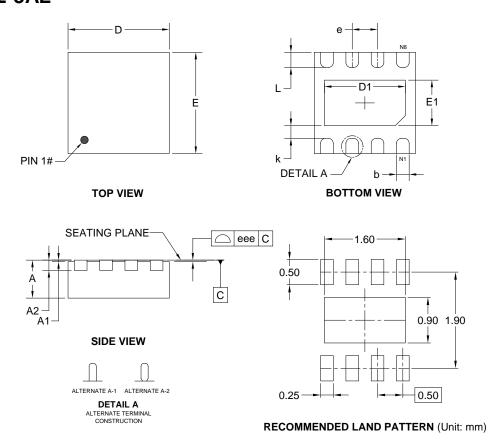

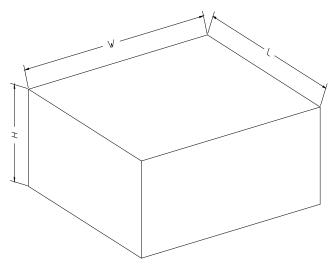

# PACKAGE OUTLINE DIMENSIONS TDFN-2×2-8AL

| Symbol | Dir   | Dimensions In Millimeters |       |  |  |  |

|--------|-------|---------------------------|-------|--|--|--|

| Symbol | MIN   | MOD                       | MAX   |  |  |  |

| Α      | 0.700 | 0.750                     | 0.800 |  |  |  |

| A1     | 0.000 | -                         | 0.050 |  |  |  |

| A2     |       | 0.203 REF                 |       |  |  |  |

| b      | 0.200 | 0.250                     | 0.300 |  |  |  |

| D      | 1.900 | 2.000                     | 2.100 |  |  |  |

| D1     | 1.450 | 1.600                     | 1.700 |  |  |  |

| Е      | 1.900 | 2.000                     | 2.100 |  |  |  |

| E1     | 0.750 | 0.900                     | 1.000 |  |  |  |

| k      | 0.150 | 0.250                     | 0.350 |  |  |  |

| е      | 0.450 | 0.500                     | 0.550 |  |  |  |

| L      | 0.200 | 0.300                     | 0.400 |  |  |  |

| eee    | 0.080 |                           |       |  |  |  |

NOTE: This drawing is subject to change without notice.

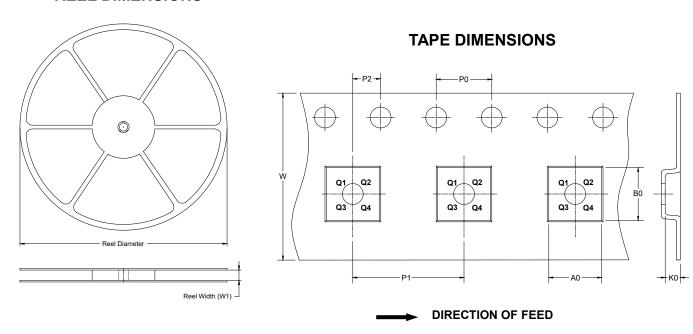

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-2×2-8AL | 7"               | 9.5                      | 2.30       | 2.30       | 1.10       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |