# Dual Ultra-Low On-Resistance Load Switch with Controlled Turn-On

#### **Features**

- Integrated Dual Channel Load Switch

- Input Voltage Range: 0.8V to 5.5V

- Dual Ultra-low ON-Resistance (16mΩ)

- $R_{DS(on)} = 17m\Omega$  at  $V_{IN} = 5V$  ( $V_{BIAS} = 5V$ )

- $R_{DS(on)} = 16m\Omega$  at  $V_{IN} = 3.6V$  ( $V_{BIAS} = 5V$ )

- $R_{DS(on)} = 16m\Omega$  at  $V_{IN} = 1.8V$  ( $V_{BIAS} = 5V$ )

- $R_{DS(on)} = 15m\Omega$  at  $V_{IN} = 0.8V$  ( $V_{BIAS} = 5V$ )

- 6A Continuous Switch Current per channel

- Low Quiescent Current

- 65µA (Both Channel)

- 55µA (Single Channel)

- Low Threshold Control Inputs

- Adjustable Slew-rate Control

- Quick Output Discharge Transistor

- 14 Pin TDFN Package with Thermal Pad

## **General Description**

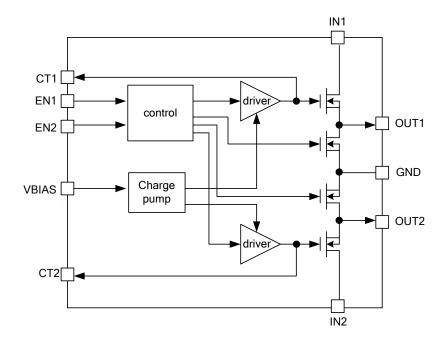

The G2898 is dual N-channel MOSFET power switch designed for high-side load-switching application. The device has a typical  $R_{\text{DS(ON)}}$  of  $16\mathrm{m}\,\Omega$  and the output current is limited to 6A. Each channel is controlled by an on/off input (EN1, EN2) independently, which is suitable for interfacing directly with low-voltage I/O ports.

In the G2898, a  $220\Omega$  on-chip load resistor is added for quick output discharge (QOD) when the switch is turned off. Moreover, the controlled rise time can be adjusted by using a ceramic capacitor on the CTx pins in order to prevent in-rush current at start-up time.

The G2898 is available in 14 pin TDFN package.

## **Applications**

- Notebooks / Netbooks

- Tablet PCs

- **■** Consumer Electronics

- Set-Top-Boxes

- Industrial Systems

- Telecom Systems

## **Ordering Information**

| ORDER<br>NUMBER | MARKING | TEMP.<br>RANGE | PACKAGE<br>(Green) |  |

|-----------------|---------|----------------|--------------------|--|

| G2898KD1U       | 2898    | -40°C to 85°C  | TDFN2X3-14         |  |

Note: KD: TDFN2X3-14 1: Bonding Code U: Tape & Reel

Green: Lead Free / Halogen Free.

#### G2898

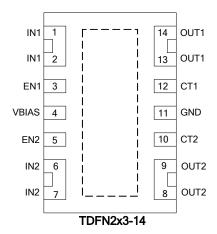

## Pin Configuration

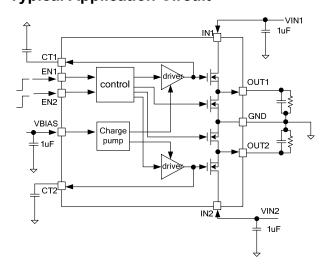

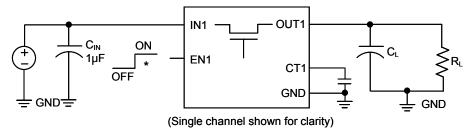

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| $V_{IN1}$ , $V_{IN2}$ to GND0.3V to +6V                     | Continuous Power Dissipation $(T_A = +25^{\circ}C)^*$ |

|-------------------------------------------------------------|-------------------------------------------------------|

| EN1,EN2 to GND0.3V to +6V                                   | TDFN2X3-14                                            |

| $V_{OUT1}$ , $V_{OUT1}$ to GND0.3V to +6V                   | Thermal Resistance Junction to Case, $(\theta_{JC})$  |

| CT1,CT2 to GND0.3V to +12V                                  | TDFN2X3-14                                            |

| V <sub>BIAS</sub> to GND0.3V to +6V                         | Operating Temperature Range40°C to 85°C               |

| Continuous Switch Current (I <sub>MAX</sub> ) 6A            | Storage Temperature Range65°C to 150°C                |

| Junction Temperature                                        | Reflow Temperature (soldering, 10sec)                 |

| Thermal Resistance Junction to Ambient, (θ <sub>JA</sub> )* | ESD(HBM)                                              |

| TDFN2X3-14                                                  | ESD(MM)                                               |

|                                                             |                                                       |

<sup>\*</sup>Please refer to Minimum Footprint PCB Layout Section

Note 1 : Human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

## **Recommended Operating Conditions**

| PARAMETER                              | MIN      | MAX        | UNITS          |

|----------------------------------------|----------|------------|----------------|

| VIN1,2 Input voltage range             | 0.8      | $V_{BIAS}$ | <sub>P</sub> V |

| VBIAS Bias voltage range               | 2,5      | 5.6        | ٧              |

| EN1,2 ON voltage range                 | 0        | 5.5        | V              |

| VOUT1,2 Output voltage range           | <u> </u> | VIN1,2     | V              |

| VIH High-level input voltage, EN1, EN2 | 1.2      | 5.5        | V              |

| VIL Low-level input voltage, EN1, EN2  |          | 0.5        | V              |

| CIN1,2 Input Capacitor                 | 1*       |            | μF             |

<sup>\*</sup>Note: 1-uF input capacitor is sufficient in most application cases. If the distance of power trace on PCB is longer than general design, larger input capacitor is highly recommended for normal operation.

### **Electrical Characteristics**

$(V_{IN1} = 0.8V \text{ to } 5.5V, V_{IN2} = 0.8V \text{ to } 5.5V, V_{BIAS} = 5V, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

| PARAMETER                    | SYMBOL               | Condi                                                                          | tions       | $T_A$ | MIN | TYP | MAX        | UNITS |

|------------------------------|----------------------|--------------------------------------------------------------------------------|-------------|-------|-----|-----|------------|-------|

| Input Voltage Range          | $V_{IN}$             |                                                                                |             |       | 0.8 |     | $V_{BIAS}$ | V     |

| Bias Voltage Range           | $V_{BIAS}$           |                                                                                |             |       | 2.5 |     | 5.6        | V     |

|                              | •                    | IOUT1 = IOUT2 = 0,<br>VIN1 = VIN2 =5V<br>EN1 =EN2=V <sub>BIAS</sub> =5V        |             | Full  |     | 65  | 80         | μA    |

|                              |                      | IOUT1 = IOUT2 = 0,<br>VIN1 = VIN2 =5V<br>EN1 = V <sub>BIAS</sub> = 5V, EN      |             | Full  |     | 53  |            | μΑ    |

| Bias Current                 | I <sub>BIAS</sub>    | IOUT1 = IOUT2 = 0,<br>VIN1 = VIN2 =2.5V<br>EN1 =EN2=V <sub>BIAS</sub> =2.5V    |             | Full  |     | 40  | 48         | μΑ    |

|                              |                      | IOUT1 = IOUT2 = 0,<br>VIN1 = VIN2 =2.5V<br>EN1 = V <sub>BIAS</sub> = 2.5V, EN2 |             | Full  |     | 33  |            | μΑ    |

| Shutdown Bias Current        | I <sub>SHDN</sub>    | ENx = GND, VOUTx = 0V                                                          |             | Full  |     |     | 1          | μΑ    |

| Off-state Supply Current     | I <sub>IN_OFF</sub>  | ENx = GND, VOUTx = 0V,<br>VINx= 0.8 to 5V                                      |             | Full  |     | 0.5 | 8          | μΑ    |

| EN pin Input leakage Current | I <sub>EN_LEAK</sub> | EN=5.5V                                                                        |             | Full  |     |     | 1          | μΑ    |

|                              |                      |                                                                                | VINx=5V     | 25 °C |     | 17  | 23         |       |

|                              |                      |                                                                                | VIIVX-5V    | Full  |     |     | 27         | mΩ    |

|                              |                      | Enx = VBIAS,                                                                   | VINx=3.6V   | 25 °C |     | 16  | 23         |       |

| On -Resistance               |                      | IOUTx = -200mA                                                                 | VIIVX-3.0V  | Full  |     |     | 27         |       |

| OII -Nesistance              | R <sub>DS(on)</sub>  | VBIAS = 5V,                                                                    | VINx=1.8V   | 25 °C |     | 16  | 23         |       |

|                              |                      |                                                                                | V 11VX-1.0V | Full  |     |     | 27         |       |

|                              |                      |                                                                                | VINx=0.8V   | 25 °C |     | 15  | 23         |       |

|                              |                      |                                                                                | VINX=U.8V   |       |     |     | 27         |       |

Electrical Characteristics (Continued)  $(V_{IN1} = 0.8V \text{ to } 5.5V, V_{IN2} = 0.8V \text{ to } 5.5V, V_{BIAS} = 5V, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ (unless otherwise noted)}$

| PARAMETER                          | SYMBOL              | Condition                         | ons           | T <sub>A</sub> | MIN | TYP | MAX | UNITS |

|------------------------------------|---------------------|-----------------------------------|---------------|----------------|-----|-----|-----|-------|

|                                    |                     |                                   | \/INI0        | 25 °C          |     | 18  | 25  |       |

|                                    |                     |                                   | VINx=2.5V     | Full           | -   |     | 30  |       |

|                                    |                     | Enx =VBIAS,                       | \/INI\v=4_0\/ | 25 °C          |     | 17  | 25  | mΩ    |

| On -Resistance                     | D                   | IOUTx = -200mA                    | VINx=1.8V     | Full           |     |     | 30  |       |

| OII -Resistance                    | R <sub>DS(on)</sub> | VBIAS = 2.5V,                     | VINx=1.2V     | 25 °C          |     | 16  | 25  |       |

|                                    |                     |                                   |               | Full           |     |     | 30  |       |

|                                    |                     |                                   |               | 25 °C          |     | 15  | 25  |       |

|                                    |                     |                                   | VINx=0.8V     | Full           |     |     | 30  |       |

| Discharge Resistance               | R <sub>DIS</sub>    | VINx = 5.0V,ENx = 0V, IOUTx = 1mA |               | Full           |     | 250 | 450 | Ω     |

| High level input voltage on EN pin | VIH                 |                                   |               |                | 1.2 | 4   | 5.5 | V     |

| Low level input voltage on EN pin  | VIL                 |                                   |               |                |     | 0   | 0.5 | V     |

| Over Temperature Threshold         | ОТ                  | _                                 |               |                | #   | 155 |     | ့င    |

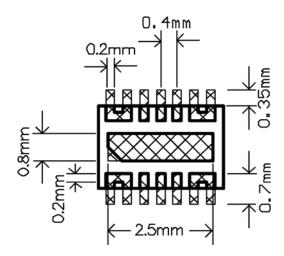

## **Minimum Footprint PCB Layout Section**

## **TDFN2X3-14**

## Pin Description

| PIN NO. | PIN NAME    | I/O | DESCRIPTION                                                           |

|---------|-------------|-----|-----------------------------------------------------------------------|

| 1       | IN1         | _   | Switch1 Input                                                         |

| 2       | IN1         | _   | Switch1 Input                                                         |

| 3       | EN1         | Ι   | Switch 1 Control Input                                                |

| 4       | VBIAS       | Ι   | Input Bias Supply                                                     |

| 5       | EN2         | _   | Switch 2 Control Input                                                |

| 6       | IN2         | _   | Switch 2 Input                                                        |

| 7       | IN2         | _   | Switch 2 Input                                                        |

| 8       | OUT2        | 0   | Switch 2 Output                                                       |

| 9       | OUT2        | 0   | Switch 2 Output                                                       |

| 10      | CT2         | 0   | Switch2 Ramp capacitor input                                          |

| 11      | GND         | ı   | Ground                                                                |

| 12      | CT1         | 0   | Switch 1 Ramp capacitor input                                         |

| 13      | OUT1        | 0   | Switch 1 Output                                                       |

| 14      | OUT1        | 0   | Switch 1 Output                                                       |

| 15      | Thermal Pad | 0   | Exposed Pad to alleviate thermal stress. Solder to GND in PCB layout. |

## **Block Diagram**

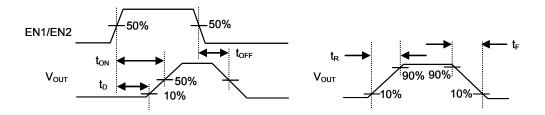

## **Parametric Measurement Information**

**Test Circuit**

$t_{\text{ON}}$  /  $t_{\text{OFF}}$  WAVEFORMS

\*. Rising and falling time of control signal EN1,EN2 is 100ns

Figure 1. Test Circuit and  $t_{\text{ON}}$  /  $t_{\text{OFF}}$  Waveforms

## **SWITCHING CHARATERISTICS**

| PARAME                              | ETER                                                                                                               | MIN | TYP  | MAX | UNIT |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|--|

| V <sub>IN</sub> =V <sub>EN</sub> =V | / <sub>BIAS</sub> =5V, T <sub>A</sub> =25°C (unless otherwise noted)                                               |     |      |     |      |  |  |

| ton                                 | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 1210 |     |      |  |  |

| t <sub>OFF</sub>                    | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 1    |     |      |  |  |

| t <sub>R</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 1600 |     | μs   |  |  |

| t <sub>F</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 2    |     |      |  |  |

| $t_D$                               | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 410  |     |      |  |  |

| V <sub>IN</sub> =0.8V, V            | V <sub>EN</sub> =V <sub>BIAS</sub> =5V, T <sub>A</sub> =25°C (unless otherwise noted)                              |     |      |     |      |  |  |

| t <sub>ON</sub>                     | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 440  |     |      |  |  |

| t <sub>OFF</sub>                    | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 1    |     |      |  |  |

| t <sub>R</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 315  |     | μs   |  |  |

| t <sub>F</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 3    |     |      |  |  |

| t <sub>D</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 280  |     |      |  |  |

| V <sub>IN</sub> =2.5V, V            | V <sub>EN</sub> =5V, V <sub>BIAS</sub> =2.5V, T <sub>A</sub> =25°C (unless otherwise noted)                        |     |      |     | _    |  |  |

| t <sub>ON</sub>                     | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 790  |     |      |  |  |

| t <sub>OFF</sub>                    | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 2    |     |      |  |  |

| t <sub>R</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 870  |     | μs   |  |  |

| t <sub>F</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 3    |     |      |  |  |

| t <sub>D</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 360  |     |      |  |  |

| V <sub>IN</sub> =0.8V, V            | V <sub>IN</sub> =0.8V, V <sub>EN</sub> =5V, V <sub>BIAS</sub> =2.5V, T <sub>A</sub> =25°C (unless otherwise noted) |     |      |     |      |  |  |

| t <sub>ON</sub>                     | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 460  |     |      |  |  |

| t <sub>OFF</sub>                    | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 2    |     |      |  |  |

| t <sub>R</sub>                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 330  |     | μs   |  |  |

| $t_{\text{F}}$                      | $R_L=10\Omega$ , $C_L=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 3    |     |      |  |  |

| t <sub>D</sub>                      | $R_1=10\Omega$ , $C_1=0.1\mu F$ , $C_T=1000pF$                                                                     |     | 300  |     |      |  |  |

## **Application Information**

### VIN and VBIAS voltage range

For optimal  $R_{DS(on)}$  performance, make sure  $V_{IN} \leq V_{BIAS}$ . The device will still be functional if  $V_{IN} > V_{BIAS}$  but it will exhibit  $R_{DS(on)}$  greater than what is listed in the Electrical characteristics table. See Figure below for an example for a typical device. Notice the increasing  $R_{DS(on)}$  as  $V_{IN}$  exceeds  $V_{BIAS}$  voltage. Be sure to never exceed the maximum voltage rating for  $V_{IN}$  and  $V_{BIAS}$ .

## R<sub>ON</sub> vs. V<sub>IN</sub>(VIN>VBIAS, SINGLE CHANNEL) VBIAS=2.5V 47 VBIAS=3.3V VBIAS=3.6V 42 VBIAS=4.2V VBIAS=5V 37 VBIAS=5.5V © 32 № 27 Temperature=25oC,IOUT=-200mA 22 17 12 0.8 1.2 1.6 2 2.4 2.8 3.2 3.6 4 4.4 4.8 5.2 5.6 VIN(V)

Figure 2. R<sub>DS(on)</sub> vs. V<sub>IN</sub> (V<sub>IN</sub>>V<sub>BIAS</sub> Single Channel)

### Adjustable rise time

A capacitor to GND on the CT pins sets the slew rate for each channel. To ensure desired performance, a capacitor with a minimum voltage rating of 25V should be used on the CT pin. An approximate formula for the relationship between CT and slew rate is (the equation below accounts for 10% to 90% measurement on VOUT and does NOT apply for CT = 0pF. Use table below to determine rise times for when CT=0pF):

SR = 0.37×CT+17.8

Where,

SR = slew rate (in  $\mu$ s/V)

CT = the capacitor value on the CT pin (in pF)

The units for the constant 17.8 is in  $\mu$ s/V.

Rise time can be calculated by multiplying the input voltage by the slew rate. The table below contains rise time values measured on a typical device. Rise times shown below are only valid for the power-up sequence where  $V_{IN}$  and  $V_{BIAS}$  are already in steady state condition and the EN pin is asserted high.

| CTx(pF)    |       | Rise tim |      | 90%, C <sub>L</sub> =0.1µ<br>lues at 25°C, | F, C <sub>IN</sub> =1µF, R<br>V <sub>BIAS</sub> =5V | L=10Ω |      |

|------------|-------|----------|------|--------------------------------------------|-----------------------------------------------------|-------|------|

| O : X(p: ) | 5V    | 3.3V     | 1.8V | 1.5V                                       | 1.2V                                                | 1.05V | 0.8V |

| 0          | 99    | 72       | 50   | 44                                         | 39                                                  | 36    | 32   |

| 220        | 496   | 338      | 198  | 170                                        | 142                                                 | 128   | 103  |

| 470        | 920   | 616      | 348  | 298                                        | 246                                                 | 220   | 177  |

| 1000       | 1708  | 1148     | 658  | 556                                        | 456                                                 | 408   | 328  |

| 2200       | 4250  | 2770     | 1550 | 1290                                       | 1052                                                | 940   | 736  |

| 4700       | 8520  | 5680     | 3160 | 2650                                       | 2160                                                | 1910  | 1520 |

| 10000      | 18400 | 12280    | 6860 | 5760                                       | 4700                                                | 4230  | 3360 |

## **Application Information**

### Input capacitor (optional)

To limit the voltage drop on the input supply caused by transient in-rush currents when the switch turns on into a discharge load capacitor or short-circuit, a capacitor need to be placed between  $V_{IN}$  and GND. A  $1\mu F$  ceramic capacitor,  $C_{IN}$ , placed close to the pins, is usually sufficient. Higher values of  $C_{IN}$  can be used to further reduce the voltage drop during high-current application. When switching heavy loads, it is recommended to have an input capacitor about 10 times higher than the output capacitor to avoid excessive voltage drop.

#### **Output capacitor (optional)**

Due to the integrated body diode in the NMOS switch, a CIN greater than CL is highly recommended. A  $C_L$  greater than  $C_{IN}$  can cause  $V_{OUT}$  to exceed  $V_{IN}$  when the system supply is removed. This could result in current flow through the body diode from  $V_{OUT}$  to  $V_{IN}$ . A  $C_{IN}$  to  $C_L$  ratio of 10 to 1 is recommended for minimizing  $V_{IN}$  dip caused by inrush currents during startup, however a 10 to 1 ratio for capacitance in not required for proper functionality of the device. A ratio smaller than 10 to 1 (such as 1 to 1) could cause slightly more  $V_{IN}$  dip upon turn due to inrush currents. This can be mitigated by increasing the capacitance on the CT pin for a longer rise time.

## **PCB Layout Guidelines**

- 1. To have lower voltage drop in field application, short and wide PCB trace is recommended. The IN/OUT pins are located in corner of IC. It is beneficial to route a wide and short PCB trace.

- 2. To absorb voltage bounce that is caused by parasitic inductor of PCB trace at quick load transient, placing Cin /Cout close to IN/OUT pin of IC is recommended.

- The wide trace of Vin/VOUT and GND can help minimize the parasitic electrical effects and the case to ambient thermal impedance. Using thermal vias located under the exposed thermal pad helps thermal dissipation of the device

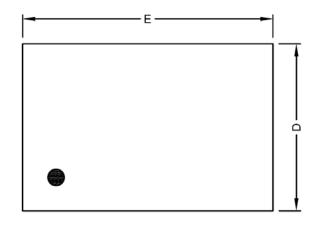

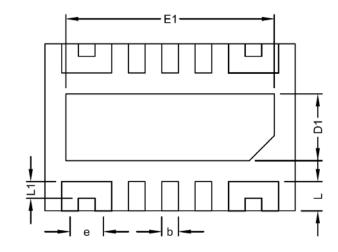

## Package Information

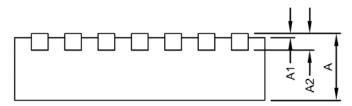

TDFN2X3-14 Package

| Or marks at | Г        | DIMENSION IN MI | И    | D      | IMENSION IN INC | н      |

|-------------|----------|-----------------|------|--------|-----------------|--------|

| Symbol      | MIN.     | NOM.            | MAX. | MIN.   | NOM.            | MAX.   |

| Α           | 0.70     | 0.75            | 0.80 | 0.0276 | 0.0295          | 0.0315 |

| A1          | 0.00     |                 | 0.05 | 0.0000 |                 | 0.0020 |

| A2          | 0.20 REF |                 |      |        | 0.0079 REF      |        |

| D           | 1.95     | 2.00            | 2.05 | 0.0768 | 0.0787          | 0.0807 |

| E           | 2.95     | 3.00            | 3.05 | 0.1161 | 0.1181          | 0.1201 |

| D1          | 0.75     | 0.85            | 0.95 | 0.0295 | 0.0335          | 0.0374 |

| E1          | 2.45     | 2.50            | 2.55 | 0.0965 | 0.0984          | 0.1004 |

| b           | 0.15     | 0.20            | 0.25 | 0.0059 | 0.0079          | 0.0098 |

| е           | 0.40 BSC |                 |      |        | 0.0157 BSC      |        |

| L           | 0.30     | 0.35            | 0.40 | 0.0118 | 0.0138          | 0.0157 |

| L1          |          | 0.20 BSC        |      |        | 0.0079 BSC      |        |

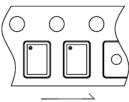

## **Taping Specification**

Feed Direction

| PACKAGE    | Q'TY/BY REEL |

|------------|--------------|

| TDFN2X3-14 | 3,000 ea     |