# TLV743P 300-mA, Low-Dropout Regulator

#### 1 Features

- Input Voltage Range: 1.4 V to 5.5 V

- Stable Operation With 1-μF Ceramic Output Capacitor

- Foldback Overcurrent Protection

- Packages:

- SOT-23 (5)

- X2SON (4)

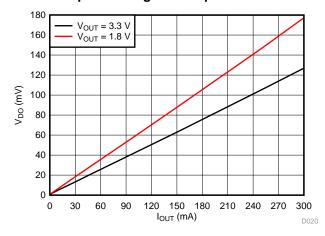

- Very Low Dropout: 125 mV at 300 mA (3.3 V<sub>OUT</sub>)

- Accuracy: 1% (Typical), 1.4% (Maximum)

- Low I<sub>Q</sub>: 34 μA

- Available in Fixed-Output Voltages:

1 V to 3.3 V

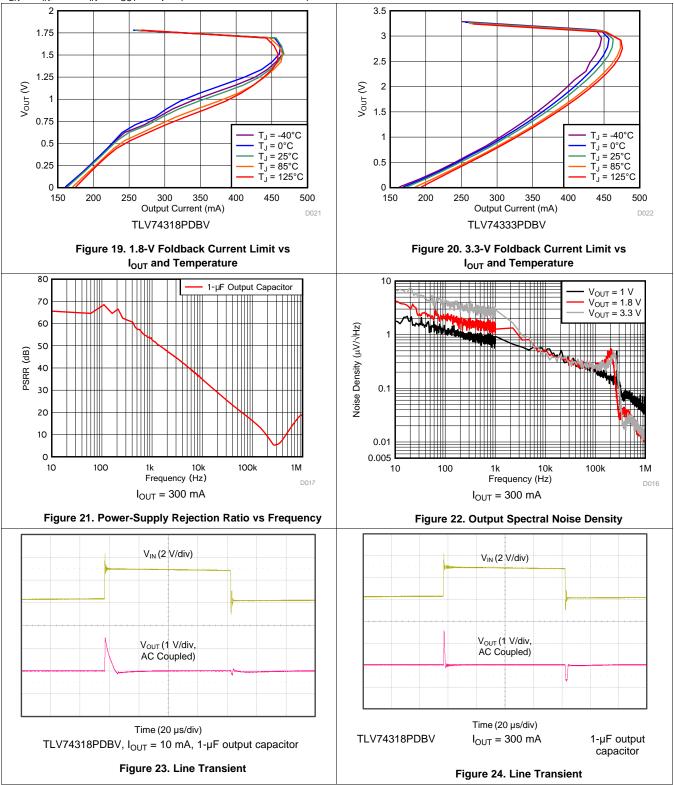

- High PSRR: 50 dB at 1 kHz

- · Active Output Discharge

## 2 Applications

- Tablets

- Smartphones

- Notebook and Desktop Computers

- Portable Industrial and Consumer Products

- WLAN and Other PC Add-On Cards

- Camera Modules

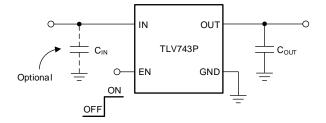

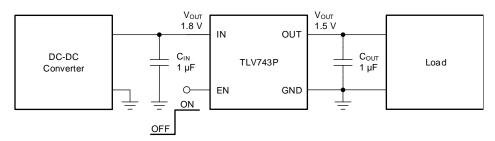

## **Typical Application Circuit**

## 3 Description

The TLV743P low-dropout linear regulator (LDO) is an ultra-small, low quiescent current LDO that sources 300 mA with good line and load transient performance. The device provides a typical accuracy of 1%.

The TLV743P is designed to be stable with a small output capacitor with a value of 1  $\mu$ F. The TLV743P device provides foldback current control during device power up and enabling. This functionality is especially important in battery-operated devices.

The TLV743P provides an active pulldown circuit to quickly discharge output loads when the device is disabled.

The TLV743P is available in standard DBV (SOT-23) and DQN (X2SON) packages.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TI.) /7.40D | SOT-23 (5) | 2.90 mm × 1.60 mm |

| TLV743P     | X2SON (4)  | 1.00 mm × 1.00 mm |

For all available packages, see the package option addendum at the end of the data sheet.

#### **Dropout Voltage vs Output Current**

## **Table of Contents**

|    | 1 Features                                                                 | 1                      | 8          | Application and Implementation                   | 16   |

|----|----------------------------------------------------------------------------|------------------------|------------|--------------------------------------------------|------|

| :  | 2 Applications                                                             | 1                      |            | 8.1 Application Information                      | 16   |

| ;  | 3 Description                                                              | 1                      |            | 8.2 Typical Application                          | 18   |

|    | 4 Revision History                                                         | 2                      | 9          | Power Supply Recommendations                     | 19   |

| ;  | 5 Pin Configuration and Functions                                          | 4                      | 10         | •                                                |      |

| (  | 6 Specifications                                                           | 5                      |            | 10.1 Layout Guidelines                           |      |

|    | 6.1 Absolute Maximum Ratings                                               | 5                      |            | 10.2 Layout Examples                             |      |

|    | 6.2 ESD Ratings                                                            | 5                      | 11         | Device and Documentation Support                 |      |

|    | 6.3 Recommended Operating Conditions                                       |                        |            | 11.1 Device Support                              |      |

|    | 6.4 Thermal Information                                                    |                        |            | 11.2 Documentation Support                       |      |

|    | 6.5 Electrical Characteristics                                             |                        |            | 11.3 Receiving Notification of Documentation Upo |      |

|    | 6.6 Typical Characteristics                                                |                        |            | 11.4 Community Resources                         |      |

|    | 7 Detailed Description                                                     |                        |            | 11.6 Electrostatic Discharge Caution             |      |

|    | 7.1 Overview                                                               |                        |            | 11.7 Glossary                                    |      |

|    | 7.2 Functional Block Diagram                                               |                        | 12         |                                                  |      |

|    | 7.3 Feature Description                                                    |                        |            | Information                                      | 21   |

| 4  | Revision History                                                           |                        |            |                                                  |      |

| Ch | anges from Revision B (March 2018) to Revis                                | ion C                  |            |                                                  | Page |

| •  | Changed description of EN pin in Pin Functions                             | table                  |            |                                                  | 4    |

| •  | Deleted typical specification from $V_{\text{EN(HI)}}$ and $V_{\text{El}}$ |                        |            |                                                  |      |

| •  | Added maximum specification to I <sub>LIM</sub> parameter                  | ` '                    |            |                                                  |      |

|    |                                                                            |                        |            |                                                  |      |

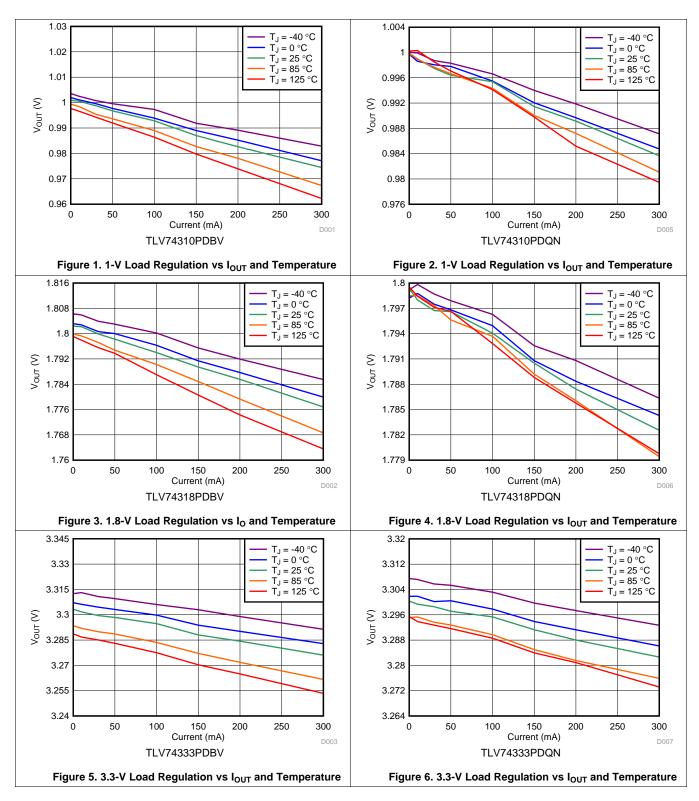

| •  | Added condition to 1-V Load Regulation vs I <sub>OUT</sub>                 |                        |            |                                                  |      |

| •  | Added condition to 1.8-V Load Regulation vs $I_{Ol}$                       |                        |            |                                                  |      |

| •  | Added condition to 3.3-V Load Regulation vs $I_{Ol}$                       | <sub>UT</sub> and Temp | erature 1  | igure                                            | 8    |

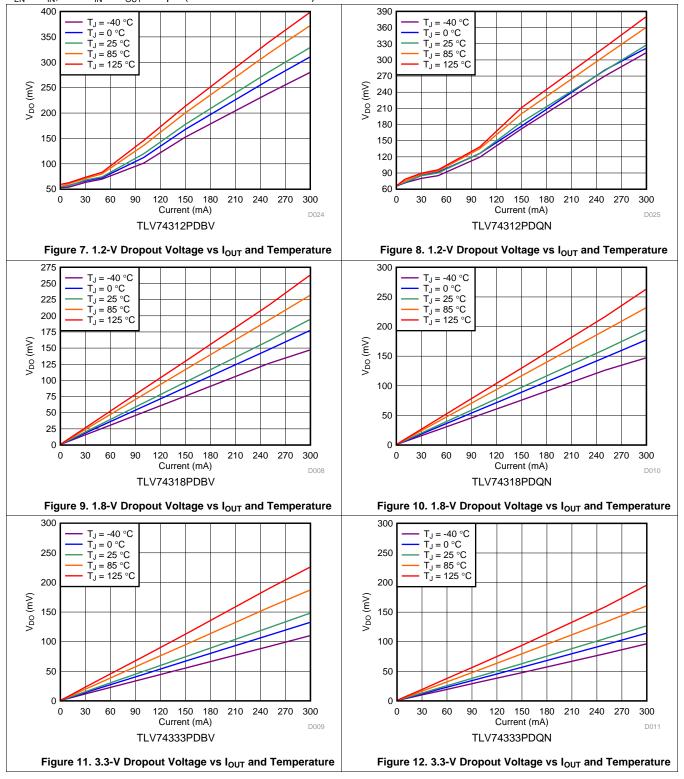

| •  | Added condition to 1.2-V Dropout Voltage vs I <sub>Ol</sub>                | <sub>JT</sub> and Temp | erature f  | igure                                            | 9    |

| •  | Added condition to 1.8-V Dropout Voltage vs Iou                            | <sub>JT</sub> and Temp | erature f  | igure                                            | 9    |

| •  | Added condition to 3.3-V Dropout Voltage vs I <sub>O</sub>                 | $_{	au}$ and Temp      | erature f  | igure                                            | 9    |

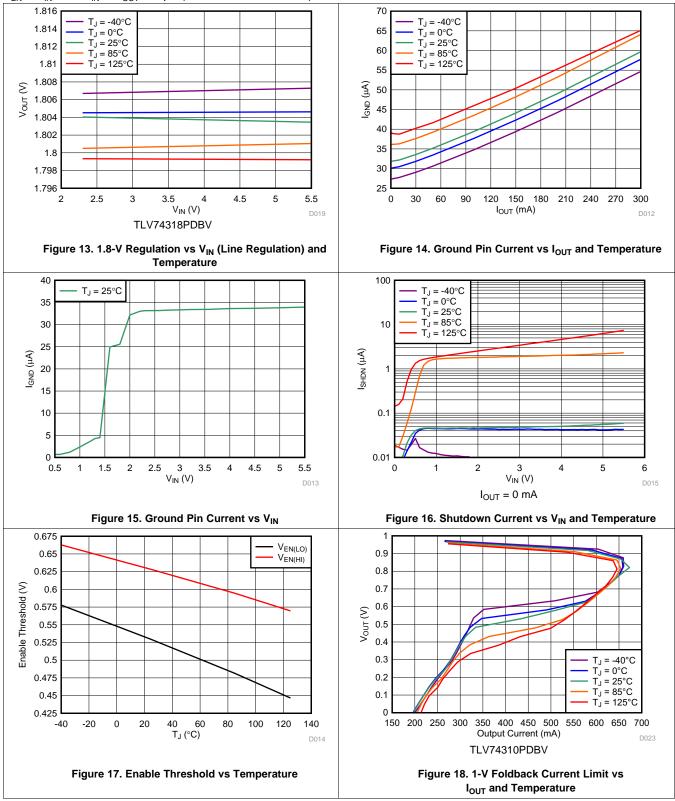

| •  | Added and Output Enable to title and changed f                             |                        |            |                                                  |      |

|    | Added DBV package to Maximum Ambient Tem                                   |                        |            | -                                                |      |

|    | -                                                                          | -                      |            |                                                  |      |

| -  | Added (3) to Device Nomenclature table                                     |                        |            |                                                  |      |

| Ch | anges from Revision A (January 2018) to Rev                                | rision B               |            |                                                  | Page |

| •  | Changed X2SON package from preview to produce                              | luction data (         | (active) . |                                                  | 1    |

|    |                                                                            |                        |            |                                                  |      |

| Ch | anges from Original (July 2017) to Revision A                              | 1                      |            |                                                  | Page |

| •  | Added X2SON package to Features list                                       |                        |            |                                                  | 1    |

| •  | Added DQN (X2SON) package to Description s                                 | ection                 |            |                                                  | 1    |

| •  | Added X2SON package to Device Information to                               |                        |            |                                                  |      |

| •  | Added DQN (X2SON) package pinout drawing a                                 |                        |            |                                                  |      |

| •  | Deleted thermal pad from DBV pinout drawing a                              |                        |            | _                                                |      |

|    | -                                                                          |                        |            |                                                  |      |

| •  | Changed format of I/O column contents and ord                              |                        |            |                                                  |      |

| •  | Added DQN (X2SON) thermal information to Th                                |                        |            |                                                  |      |

| •  | Changed condition text for Figure 31                                       |                        |            |                                                  | 17   |

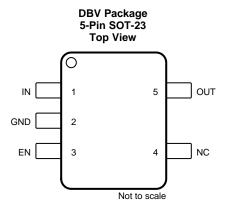

## 5 Pin Configuration and Functions

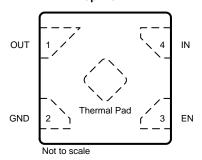

DQN Package 4-Pin X2SON With Exposed Thermal Pad Top View

## **Pin Functions**

| PIN         |        |             | 1/0 | DESCRIPTION                                                                                                                                                                               |

|-------------|--------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | SOT-23 | X2SON       | 2   | DESCRIPTION                                                                                                                                                                               |

| EN          | 3      | 3           | I   | Enable pin. Drive EN greater than $V_{\text{EN(LO)}}$ to turn on the regulator. Drive EN less than $V_{\text{EN(LO)}}$ to put the LDO into shutdown mode.                                 |

| GND         | 2      | 2           |     | Ground pin                                                                                                                                                                                |

| IN          | 1      | 4           | ı   | Input pin. A small capacitor is recommended from this pin to ground. See Input and Output Capacitor Selection for more details.                                                           |

| NC          | 4      |             |     | No internal connection                                                                                                                                                                    |

| OUT         | 5      | 1           | 0   | Regulated output voltage pin. For best transient response, use a small 1-μF ceramic capacitor from this pin to ground.  See <i>Input and Output Capacitor Selection</i> for more details. |

| Thermal pad | _      | Thermal pad | _   | The thermal pad is electrically connected to the GND node. Connect to the GND plane for improved thermal performance.                                                                     |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted); all voltages are with respect to GND<sup>(1)</sup>

|                               | • ,                                | •        |                       |      |

|-------------------------------|------------------------------------|----------|-----------------------|------|

|                               |                                    | MIN      | MAX                   | UNIT |

| Voltage                       | V <sub>IN</sub>                    | -0.3     | 6                     |      |

|                               | V <sub>EN</sub>                    | -0.3     | V <sub>IN</sub> + 0.3 | V    |

|                               | V <sub>OUT</sub>                   | -0.3     | 3.6                   |      |

| Current                       | I <sub>OUT</sub>                   | Internal | ly limited            | А    |

| Output short-circuit duration |                                    | Inde     | efinite               |      |

| Temperature                   | Operating junction, T <sub>J</sub> | -40      | 150                   | °C   |

|                               | Storage, T <sub>stg</sub>          | -65      | 160                   | 30   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Flootroototic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                      | MIN | NOM MAX  | UNIT |

|------------------|----------------------|-----|----------|------|

| $V_{IN}$         | Input range          | 1.4 | 5.5      | V    |

| $V_{OUT}$        | Output range         | 1   | 3.3      | V    |

| I <sub>OUT</sub> | Output current       | 0   | 300      | mA   |

| $V_{EN}$         | Enable range         | 0   | $V_{IN}$ | V    |

| $T_J$            | Junction temperature | -40 | 125      | °C   |

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                |        | TLV743P     |      |  |

|----------------------|----------------------------------------------|--------|-------------|------|--|

|                      |                                              |        | DQN (X2SON) | UNIT |  |

|                      |                                              | 5 PINS | 4 PINS      |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 228.4  | 218.6       | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 151.5  | 164.8       | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 55.8   | 164.9       | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 31.4   | 5.6         | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 54.8   | 163.9       | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A    | 131.4       | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

at operating temperature range ( $T_J = -40^{\circ}C$  to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5$  V or 2 V (whichever is greater),  $I_{OUT} = 1$  mA,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1$  µF (unless otherwise noted). All typical values at  $T_J = 25^{\circ}C$ .

| F                         | PARAMETER                                                                                               | TEST                                                                                                | CONDITIONS                                                                                                                        | MIN   | TYP  | MAX  | UNIT              |  |

|---------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------------------|--|

| V <sub>IN</sub>           | Input voltage                                                                                           |                                                                                                     |                                                                                                                                   | 1.4   |      | 5.5  | V                 |  |

|                           | DO 1 1                                                                                                  | T <sub>J</sub> = 25°C                                                                               |                                                                                                                                   | -1%   |      | 1%   |                   |  |

|                           | DC output accuracy                                                                                      | -40°C ≤ T <sub>J</sub> ≤ 125°C                                                                      |                                                                                                                                   | -1.4% |      | 1.4% |                   |  |

| 1\/1.0                    | Undervoltage                                                                                            | V <sub>IN</sub> rising                                                                              |                                                                                                                                   |       | 1.3  | 1.4  | V                 |  |

| JVLO                      | lockout                                                                                                 | V <sub>IN</sub> falling                                                                             |                                                                                                                                   |       | 1.25 |      | V                 |  |

| $\Delta V_{O(\Delta VI)}$ | Line regulation                                                                                         | $\Delta VI = V_{IN(nom)}$ to $V_{IN(nom)}$                                                          | + 1                                                                                                                               |       | 1    |      | mV                |  |

| A\/                       | Load regulation                                                                                         | $\Delta IO = 1 \text{ mA to } 300 \text{ mA}$                                                       | DBV poekogo                                                                                                                       |       | 16   |      | mV                |  |

| $\Delta V_{O(\Delta IO)}$ | Load regulation                                                                                         | AIO = 1 IIIA to 300 IIIA                                                                            | DBV package                                                                                                                       |       | 25   |      | IIIV              |  |

|                           |                                                                                                         |                                                                                                     | V <sub>OUT</sub> = 1.1 V<br>-40°C ≤ T <sub>J</sub> ≤ 85°C                                                                         |       |      | 480  |                   |  |

|                           |                                                                                                         |                                                                                                     | 1.2 V ≤ V <sub>OUT</sub> < 1.5 V<br>-40°C ≤ T <sub>J</sub> ≤ 85°C                                                                 |       |      | 420  |                   |  |

|                           | $V_{DO}$ Dropout voltage <sup>(1)</sup> $V_{OUT} = 0.98 \times V_{OUT(nom)}$ $I_{OUT} = 300 \text{ mA}$ | 1.5 V ≤ V <sub>OUT</sub> < 1.8 V<br>-40°C ≤ T <sub>J</sub> ≤ 85°C                                   |                                                                                                                                   |       | 370  |      |                   |  |

|                           |                                                                                                         | 1.8 V ≤ V <sub>OUT</sub> < 2.5 V<br>-40°C ≤ T <sub>J</sub> ≤ 85°C                                   |                                                                                                                                   |       | 270  |      |                   |  |

|                           |                                                                                                         |                                                                                                     | $2.5 \text{ V} \le \text{V}_{\text{OUT}} < 3.3 \text{ V}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}$ |       |      | 260  | mV                |  |

| $V_{DO}$                  |                                                                                                         |                                                                                                     | V <sub>OUT</sub> = 3.3 V<br>-40°C ≤ T <sub>J</sub> ≤ 85°C                                                                         |       | 125  | 220  |                   |  |

|                           |                                                                                                         |                                                                                                     | 1.2 V ≤ V <sub>OUT</sub> < 1.5 V<br>-40°C ≤ T <sub>J</sub> ≤ 125°C                                                                |       |      | 450  |                   |  |

|                           |                                                                                                         |                                                                                                     | 1.5 V ≤ V <sub>OUT</sub> < 1.8 V<br>-40°C ≤ T <sub>J</sub> ≤ 125°C                                                                |       |      | 400  |                   |  |

|                           |                                                                                                         |                                                                                                     | 1.8 V ≤ V <sub>OUT</sub> < 2.5 V<br>-40°C ≤ T <sub>J</sub> ≤ 125°C                                                                |       |      | 300  |                   |  |

|                           |                                                                                                         |                                                                                                     | $2.5 \text{ V} \le \text{V}_{\text{OUT}} < 3.3 \text{ V}$<br>-40°C $\le \text{T}_{\text{J}} \le 125$ °C                           |       |      | 290  |                   |  |

|                           |                                                                                                         |                                                                                                     | V <sub>OUT</sub> = 3.3 V<br>-40°C ≤ T <sub>J</sub> ≤ 125°C                                                                        |       | 125  | 270  |                   |  |

| GND                       | Ground pin current                                                                                      | I <sub>OUT</sub> = 0 mA                                                                             |                                                                                                                                   |       | 34   | 60   | μΑ                |  |

| SHDN                      | Shutdown current                                                                                        | $V_{EN} \le 0.35 \text{ V}$ $2 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ $T_{J} = 25^{\circ}\text{C}$ |                                                                                                                                   |       | 0.1  | 1    | μΑ                |  |

|                           |                                                                                                         |                                                                                                     | f = 100 Hz                                                                                                                        |       | 68   |      |                   |  |

| PSRR                      | Power-supply rejection ratio                                                                            | $V_{OUT} = 1.8 V$<br>$I_{OUT} = 300 \text{ mA}$                                                     | f = 10 kHz                                                                                                                        |       | 35   |      | dB                |  |

|                           | rejection ratio                                                                                         | 1001 - 300 1114                                                                                     | f = 100 kHz                                                                                                                       |       | 28   |      |                   |  |

| / <sub>n</sub>            | Output noise voltage                                                                                    | Bandwidth = 10 Hz to 100 $V_{OUT}$ = 1.8 V $I_{OUT}$ = 10 mA                                        | ) kHz                                                                                                                             |       | 120  |      | μV <sub>RMS</sub> |  |

| / <sub>EN(HI)</sub>       | EN pin high voltage (enabled)                                                                           |                                                                                                     |                                                                                                                                   | 0.9   |      |      | V                 |  |

| V <sub>EN(LO)</sub>       | EN pin low voltage (disabled)                                                                           |                                                                                                     |                                                                                                                                   |       |      | 0.35 | V                 |  |

| EN                        | EN pin current                                                                                          | V <sub>EN</sub> = 5.5 V                                                                             |                                                                                                                                   |       | 0.01 |      | μΑ                |  |

<sup>(1)</sup> Dropout voltage for the TLV743P is not valid at room temperature. The device engages undervoltage lockout (V<sub>IN</sub> < UVLO<sub>FALL</sub>) before the dropout condition is met.

## **Electrical Characteristics (continued)**

at operating temperature range (T $_J$  = -40°C to +125°C), V $_{IN}$  = V $_{OUT}$ (nom) + 0.5 V or 2 V (whichever is greater), I $_{OUT}$  = 1 mA, V $_{EN}$  = V $_{IN}$ , and C $_{IN}$  = C $_{OUT}$  = 1  $\mu$ F (unless otherwise noted). All typical values at T $_J$  = 25°C.

| ı                | PARAMETER                                                                                                    | TEST CONDITIONS                                                                                    | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 4                | Time from EN assertion to 98% $\times$ V <sub>OUT</sub> (nom) V <sub>OUT</sub> = 1 V I <sub>OUT</sub> = 0 mA |                                                                                                    |     | 250 |     | 5    |

| t <sub>STR</sub> | Startup time                                                                                                 | Time from EN assertion to 98% × $V_{OUT}$ (nom) $V_{OUT} = 3.3 \text{ V}$ $I_{OUT} = 0 \text{ mA}$ |     | 800 |     | μs   |

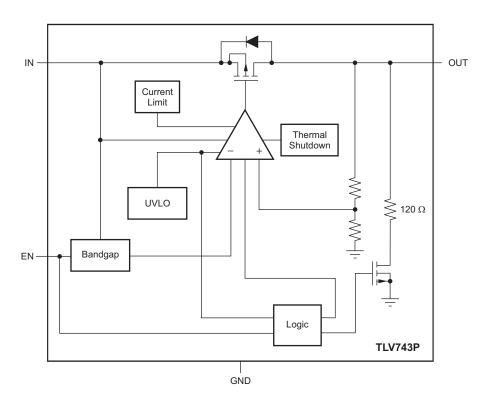

|                  | Pulldown resistor                                                                                            | V <sub>IN</sub> = 2.3 V                                                                            |     | 120 |     | Ω    |

| I <sub>LIM</sub> | Output current limit                                                                                         |                                                                                                    | 360 |     | 700 | mA   |

| l                | Short-circuit current                                                                                        | $V_{OUT}$ shorted to GND $V_{OUT} = 1 \text{ V}$                                                   |     | 150 |     | mA   |

| los              | limit                                                                                                        | $V_{OUT}$ shorted to GND $V_{OUT} = 3.3 \text{ V}$                                                 |     | 170 |     | ША   |

| _                | Thormal abutdous                                                                                             | Shutdown, temperature increasing                                                                   |     | 160 |     | °C   |

| T <sub>sd</sub>  | Thermal shutdown                                                                                             | Reset, temperature decreasing                                                                      |     | 140 |     | C    |

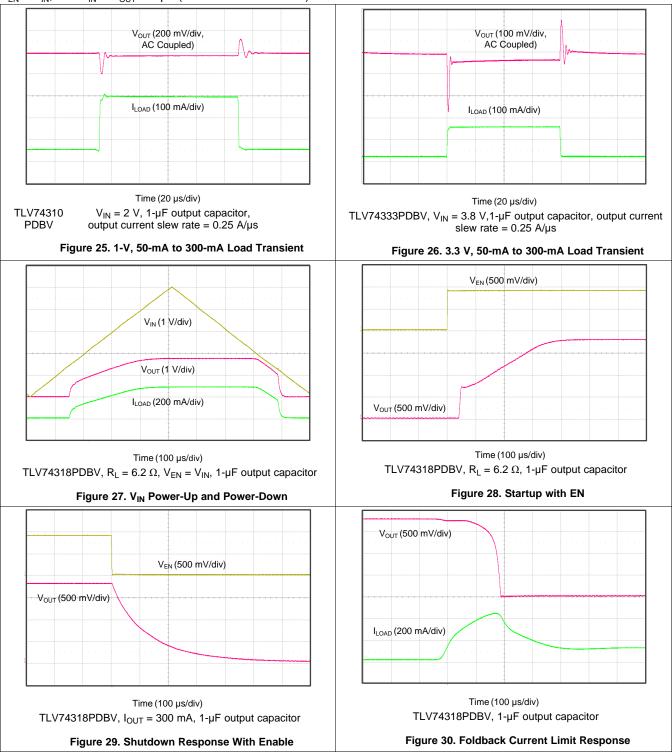

### 6.6 Typical Characteristics

at operating temperature range ( $T_J = -40$ °C to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5$  V or 2 V (whichever is greater),  $I_{OUT} = 1$  mA,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1$  µF (unless otherwise noted)

at operating temperature range ( $T_J = -40$ °C to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5$  V or 2 V (whichever is greater),  $I_{OUT} = 1$  mA,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1$  µF (unless otherwise noted)

at operating temperature range ( $T_J = -40$ °C to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5$  V or 2 V (whichever is greater),  $I_{OUT} = 1$  mA,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1$  µF (unless otherwise noted)

at operating temperature range ( $T_J = -40^{\circ}C$  to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5 \text{ V}$  or 2 V (whichever is greater),  $I_{OUT} = 1 \text{ mA}$ ,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1 \mu F$  (unless otherwise noted)

at operating temperature range ( $T_J = -40^{\circ}C$  to +125°C),  $V_{IN} = V_{OUT}(nom) + 0.5 \text{ V}$  or 2 V (whichever is greater),  $I_{OUT} = 1 \text{ mA}$ ,  $V_{EN} = V_{IN}$ , and  $C_{IN} = C_{OUT} = 1 \mu F$  (unless otherwise noted)

## 7 Detailed Description

#### 7.1 Overview

The TLV743P device belongs to a new family of next-generation, low-dropout regulators (LDOs). This device consumes low quiescent current and delivers excellent line and load transient performance. These characteristics, combined with low noise, good PSRR with low-dropout voltage, make this device well-suited for portable consumer applications.

This regulator offers foldback current limit, shutdown, and thermal protection. The operating junction temperature for this device is  $-40^{\circ}$ C to  $+125^{\circ}$ C.

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

### 7.3.1 Undervoltage Lockout (UVLO)

The TLV743P device uses an undervoltage lockout (UVLO) circuit that disables the output until the input voltage is greater than the rising UVLO voltage, UVLO<sub>RISE</sub>. This circuit makes certain that the device does not exhibit any unpredictable behavior when the supply voltage is lower than the operational range of the internal circuitry. During UVLO disable, the output connects to ground with a  $120-\Omega$  pulldown resistor.

#### 7.3.2 Shutdown and Output Enable

The enable pin (EN) is active high. Enable the device by forcing the EN pin to exceed  $V_{EN(HI)}$ . Turn off the device by forcing the EN pin to drop below  $V_{EN(LO)}$ . If shutdown capability is not required, connect EN to IN. There is no internal pulldown resistor connected to the EN pin.

The TLV743P device has an internal pulldown MOSFET that connects a  $120-\Omega$  resistor to ground when the device is disabled. The discharge time after disabling depends on the output capacitance ( $C_{OUT}$ ) and the load resistance ( $R_I$ ) in parallel with the  $120-\Omega$  pulldown resistor. The time constant is calculated in Equation 1:

$$t = \frac{120 \times R_L}{120 + R_L} \times C_{OUT} \tag{1}$$

#### 7.3.3 Internal Foldback Current Limit

The TLV743P device has an internal foldback current limit that protects the regulator during fault conditions. The current allowed through the device is reduced as the output voltage falls. When the output is shorted, the LDO supplies a typical current of 150 mA. The output voltage is not regulated when the device is in current limit. In this condition, the output voltage is the product of the regulated current and the load resistance. When the device output is shorted, the PMOS pass transistor dissipates power  $[(V_{IN} - V_{OUT}) \times I_{OS}]$  until thermal shutdown is triggered and the device turns off. After the device cools down, the internal thermal shutdown circuit turns the device back on. If the fault condition continues, the device cycles between current limit and thermal shutdown. See *Thermal Information* for more details.

The foldback current limit circuit limits the current allowed through the device to current levels lower than the minimum current limit at nominal  $V_{OUT}$  current limit ( $I_{LIM}$ ) during startup. See Figure 18 to Figure 20 for typical foldback current limit values. If the output is loaded by a constant-current load during startup, or if the output voltage is negative when the device is enabled, then the required load current by the load may exceed the foldback current limit and the device may not rise to the full output voltage. For constant current loads, disable the output load until the TLV743P has risen to the nominal output voltage.

The TLV743P PMOS pass element has an intrinsic body diode that conducts current when the voltage at the OUT pin exceeds the voltage at the IN pin. Do not force the output voltage to exceed the input voltage because excessively high current may flow through the body diode.

### 7.3.4 Thermal Shutdown

Thermal shutdown protection disables the output when the junction temperature rises to approximately 160°C. Disabling the device eliminates power dissipated by the device, which allows the device to cool. When the junction temperature cools to approximately 140°C, the output circuitry is enabled again. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits regulator dissipation, which protects the device from damage as a result of overheating.

Activating the thermal shutdown feature usually indicates excessive power dissipation as a result of the product of the  $(V_{IN} - V_{OUT})$  voltage and the load current. For reliable operation, limit junction temperature to 125°C maximum. To estimate the margin of safety in a complete design, increase the ambient temperature until the thermal protection is triggered; use worst-case loads and signal conditions.

The TLV743P internal protection circuitry protects against overload conditions, but is not intended to be active in normal operation. Continuously running the TLV743P device into thermal shutdown degrades device reliability.

#### 7.4 Device Functional Modes

### 7.4.1 Normal Operation

The device regulates to the nominal output voltage under the following conditions:

- The input voltage has previously exceeded the UVLO rising voltage and has not decreased below the UVLO falling threshold.

- The input voltage is greater than the nominal output voltage added to the dropout voltage.

- The enable voltage has previously exceeded the enable rising threshold voltage and not decreased below the enable falling threshold.

- The output current is less than the current limit.

- The device junction temperature is less than the thermal shutdown temperature.

#### 7.4.2 Dropout Operation

If the input voltage is lower than the nominal output voltage plus the specified dropout voltage, but all other conditions are met for normal operation, the device operates in dropout mode. In this condition, the output voltage is the same the input voltage minus the dropout voltage. The transient performance of the device is significantly degraded because the pass device is in a triode state and no longer controls the current through the LDO. Line or load transients in dropout may result in large output voltage deviations.

#### 7.4.3 Disabled

The device is disabled under the following conditions:

- The input voltage is less than the UVLO falling voltage, or has not yet exceeded the UVLO rising threshold.

- The enable voltage is less than the enable falling threshold voltage or has not yet exceeded the enable rising threshold.

- The device junction temperature is greater than the thermal shutdown temperature.

When the device is disabled, the active pulldown resistor discharges the output.

Table 1 lists the conditions that result in different operating modes.

**Table 1. Device Functional Mode Comparison**

| OPERATING MODE                                               | PARAMETER                                                      |                                       |                                     |                        |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|-------------------------------------|------------------------|--|--|--|

| OPERATING MODE                                               | V <sub>IN</sub>                                                | V <sub>EN</sub>                       | I <sub>OUT</sub>                    | TJ                     |  |  |  |

| Normal mode                                                  | $V_{IN} > V_{OUT}(nom) + V_{DO}$<br>and $V_{IN} > UVLO_{RISE}$ | $V_{EN} > V_{EN(HI)}$                 | I <sub>OUT</sub> < I <sub>LIM</sub> | T <sub>J</sub> < 160°C |  |  |  |

| Dropout mode                                                 | $UVLO_{RISE} < V_{IN} < V_{OUT}(nom) + V_{DO}$                 | $V_{EN} > V_{EN(HI)}$                 | I <sub>OUT</sub> < I <sub>LIM</sub> | T <sub>J</sub> < 160°C |  |  |  |

| Disabled mode<br>(any true condition<br>disables the device) | V <sub>IN</sub> < UVLO <sub>FALL</sub>                         | V <sub>EN</sub> < V <sub>EN(LO)</sub> | _                                   | T <sub>J</sub> > 160°C |  |  |  |

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

#### 8.1.1 Input and Output Capacitor Selection

The TLV743P device uses an advanced internal control loop to obtain stable operation with the use of input or output capacitors. An output capacitance of 1  $\mu$ F or larger generally provides good dynamic response. Use X5R-and X7R-type ceramic capacitors because these capacitors have minimal variation in value and equivalent series resistance (ESR) over temperature.

Although an input capacitor is not required for stability, increased output impedance from the input supply may compromise the performance of the TLV743P. Good analog design practice is to connect a 0.1- $\mu$ F to 1- $\mu$ F capacitor from IN to GND. This capacitor counteracts reactive input sources and improves transient response, input ripple, and PSRR. Use an input capacitor if the source impedance is greater than  $0.5~\Omega$ . Use a higher-value capacitor if large, fast, rise-time load transients are expected, or if the device is located several inches from the input power source.

#### 8.1.2 Dropout Voltage

The TLV743P device uses a PMOS pass transistor to achieve low dropout. When  $(V_{IN} - V_{OUT})$  is less than the dropout voltage  $(V_{DO})$ , the PMOS pass device is in the linear region of operation and the input-to-output resistance is the  $R_{DS(ON)}$  of the PMOS pass element.  $V_{DO}$  scales approximately with output current because the PMOS device behaves like a resistor in dropout mode. As with any linear regulator, PSRR and transient response degrade as  $(V_{IN} - V_{OUT})$  approaches dropout operation. See Figure 7 to Figure 12 for typical dropout values.

### **Application Information (continued)**

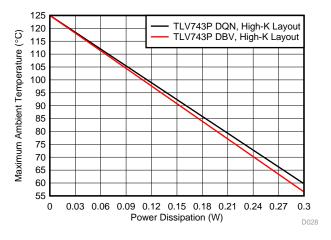

#### 8.1.3 Power Dissipation

The ability to remove heat from the die is different for each package type and presents different considerations in the printed circuit board (PCB) layout. The PCB area around the device that is free of other components moves the heat from the device to ambient air. Performance data for JEDEC high-K boards are shown in *Thermal Information*. Using heavier copper increases the effectiveness in removing heat from the device. The addition of plated through-holes to heat-dissipating layers also improves heat sink effectiveness.

Power dissipation ( $P_D$ ) depends on input voltage and load conditions.  $P_D$  is equal to the product of the output current and voltage drop across the output pass element, as shown in Equation 2.

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT}$$

(2)

Figure 31 shows the maximum ambient temperature versus the power dissipation of the TLV743P device in the DQN and DBV packages. This figure assumes the device is soldered on JEDEC standard high-K layout with no airflow over the board. Actual board thermal impedances vary widely. If the application requires high power dissipation, it is helpful to have a thorough understanding of the board temperature and thermal impedances to make certain that the TLV743P device does not operate continuously above a junction temperature of 125°C.

TLV743P, high-K layout

Figure 31. Maximum Ambient Temperature vs Device Power Dissipation

#### 8.2 Typical Application

Figure 32. DC/DC Converter Post Regulation

### 8.2.1 Design Requirements

**Table 2. Design Parameters**

| PARAMETER                          | DESIGN REQUIREMENT                           |  |  |

|------------------------------------|----------------------------------------------|--|--|

| Input voltage                      | 1.8 V, ±5%                                   |  |  |

| Output voltage                     | 1.5 V, ±1%                                   |  |  |

| Output current                     | 200-mA DC, 300-mA peak                       |  |  |

| Output voltage transient deviation | < 10%, 1-A/µs load step from 50 mA to 200 mA |  |  |

| Maximum ambient temperature        | 85°C                                         |  |  |

## 8.2.2 Detailed Design Procedure

Input and output capacitors are required to achieve the output voltage transient requirements. Capacitance values of 1  $\mu$ F are selected to give the maximum output capacitance in a small, low-cost package.

Figure 7 shows the 1.2-V option dropout voltage. Given that dropout voltages are higher for lower output-voltage options, and given that the 1.2-V option dropout voltage is typically less than 300 mV at 125°C, then the 1.5-V option dropout voltage is typically less than 300 mV at 125°C.

See Figure 31 to verify that the maximum junction temperature is not exceeded.

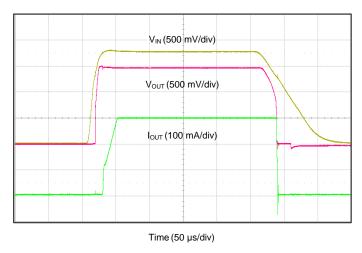

#### 8.2.3 Application Curve

Figure 33. 1.8-V to 1.5-V Regulation at 300 mA

## 9 Power Supply Recommendations

Connect a low-output impedance power supply directly to the IN pin of the TLV743P device. Inductive impedances between the input supply and the IN pin can create significant voltage excursions at the IN pin during startup or load transient events. If inductive impedances are unavoidable, use an input capacitor.

## 10 Layout

## 10.1 Layout Guidelines

- Place input and output capacitors as close as possible to the device.

- Use copper planes for device connections to optimize thermal performance.

- Place thermal vias around the device to distribute heat.

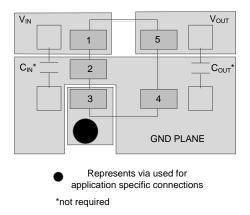

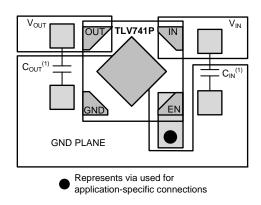

## 10.2 Layout Examples

Figure 34. Layout Example: DBV Package

(1) Not required.

Figure 35. X2SON Layout Example

### 11 Device and Documentation Support

### 11.1 Device Support

#### 11.1.1 Development Support

#### 11.1.1.1 Evaluation Module

An evaluation module (EVM) is available to assist in the initial circuit performance evaluation using the TLV743P device. The TLV73312PEVM-643 evaluation module (and related user guide) can be requested at the Texas Instruments website through the product folders or purchased directly from the TI eStore.

#### 11.1.2 Device Nomenclature

Table 3. Device Nomenclature (1)(2)

| PRODUCT                      | V <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

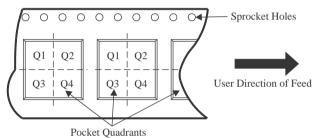

| TLV743P <b>xx(x)Pyyyz(3)</b> | <ul> <li>xx(x) is the nominal output voltage. For output voltages with a resolution of 100 mV, two digits are used in the ordering number; otherwise, three digits are used (for example, 28 = 2.8 V; 125 = 1.25 V).</li> <li>P indicates an active output discharge feature. All members of the TLV743 family will actively discharge the output when the device is disabled.</li> <li>yyy is the package designator.</li> <li>z is the package quantity. R is for reel (3000 pieces), T is for tape (250 pieces).</li> <li>(3) indicates an alternative tape and reel orientation. 3 indicates that pin 1 is in quadrant 3. See the Package Materials Information addendum for more information.</li> </ul> |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder on www.ti.com.

### 11.2 Documentation Support

#### 11.2.1 Related Documentation

TLV73312PDQN-643 Evaluation Module User Guide (SBVU024)

#### 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

<sup>(2)</sup> Output voltages from 1 V to 3.3 V in 50-mV increments are available. Contact the factory for details and availability.

#### 11.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

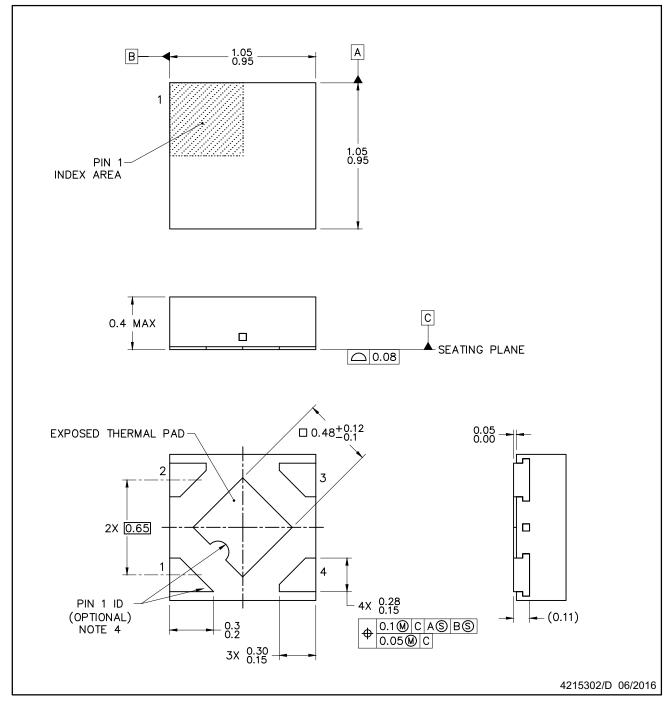

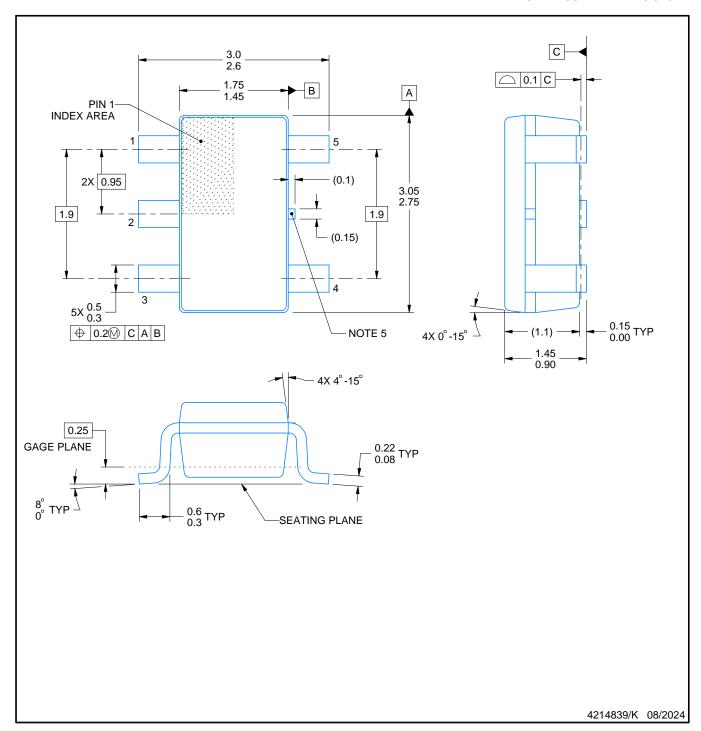

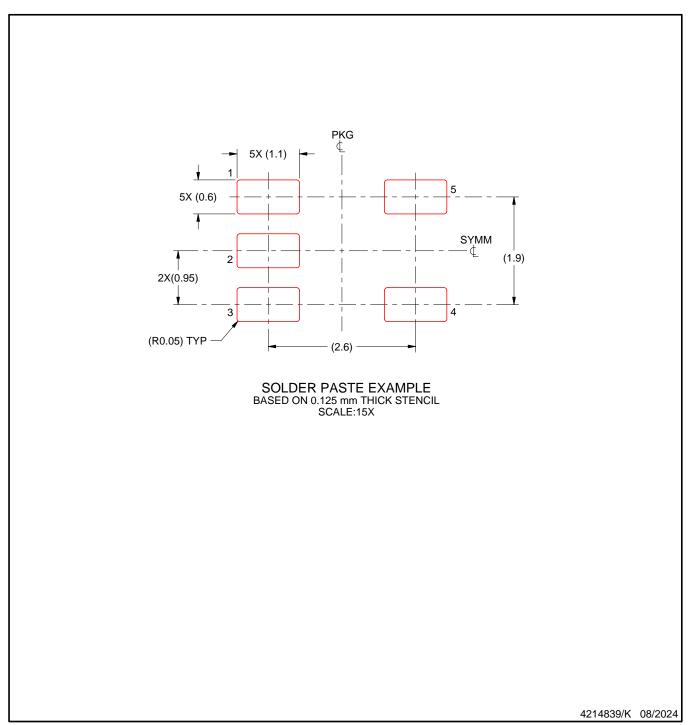

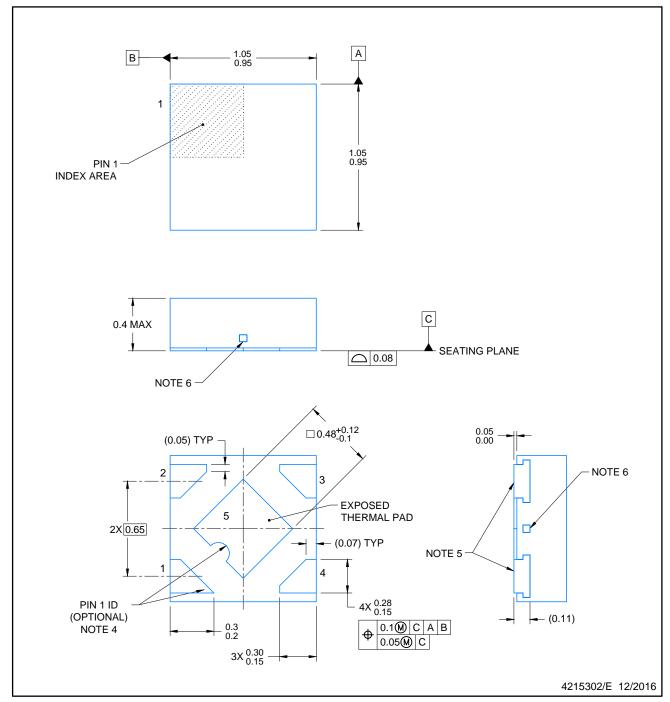

**DQN0004A**

## **PACKAGE OUTLINE**

## X2SON - 0.4 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

- 4. Features may not exist. Recommend use of pin 1 marking on top of package for orientation purposes.

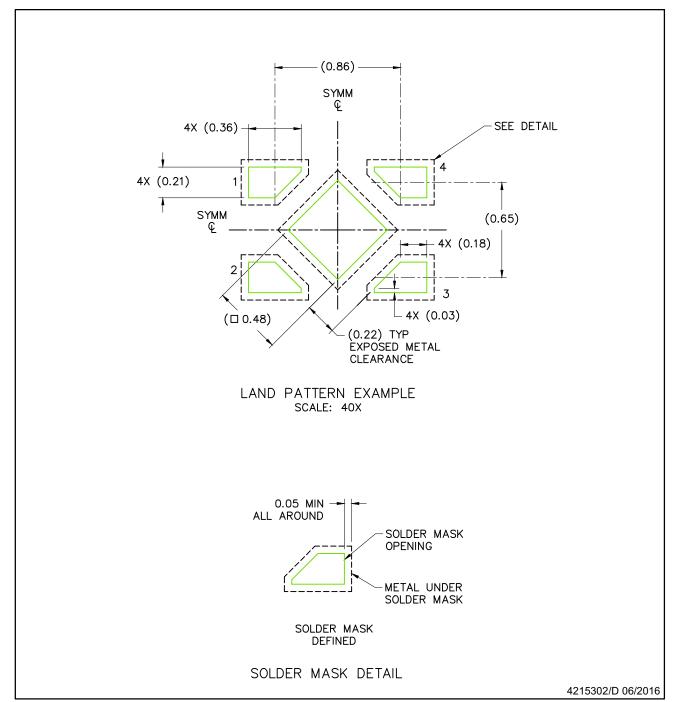

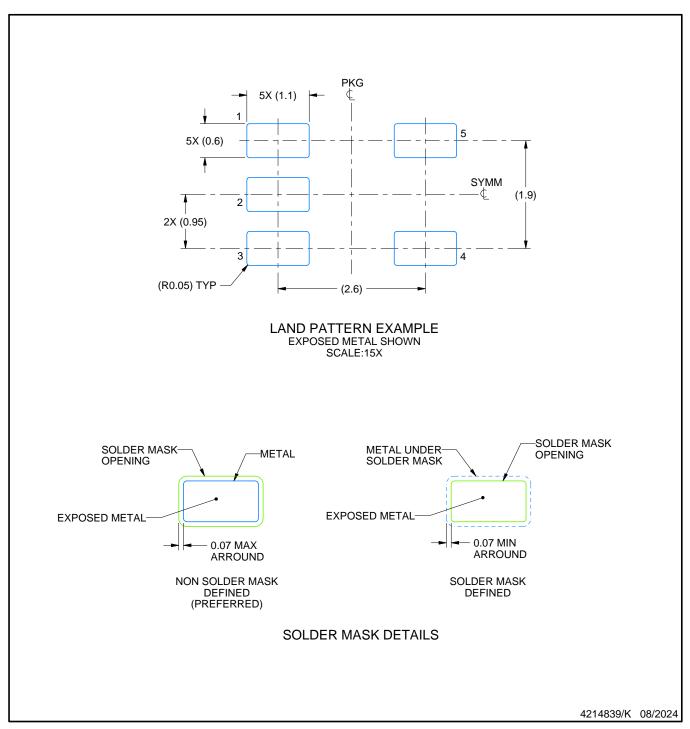

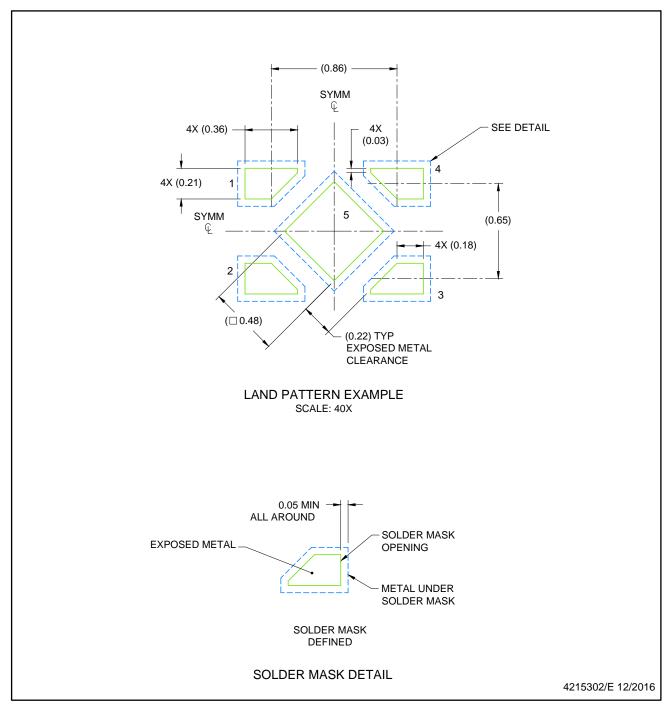

## **EXAMPLE BOARD LAYOUT**

## **DQN0004A**

## X2SON - 0.4 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 5. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 6. If any vias are implemented, it is recommended that vias under paste be filled, plugged or tented.

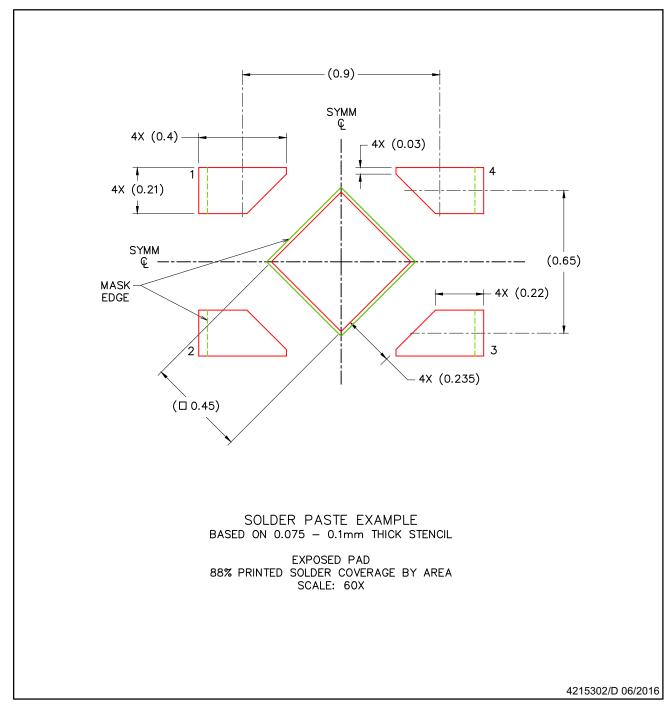

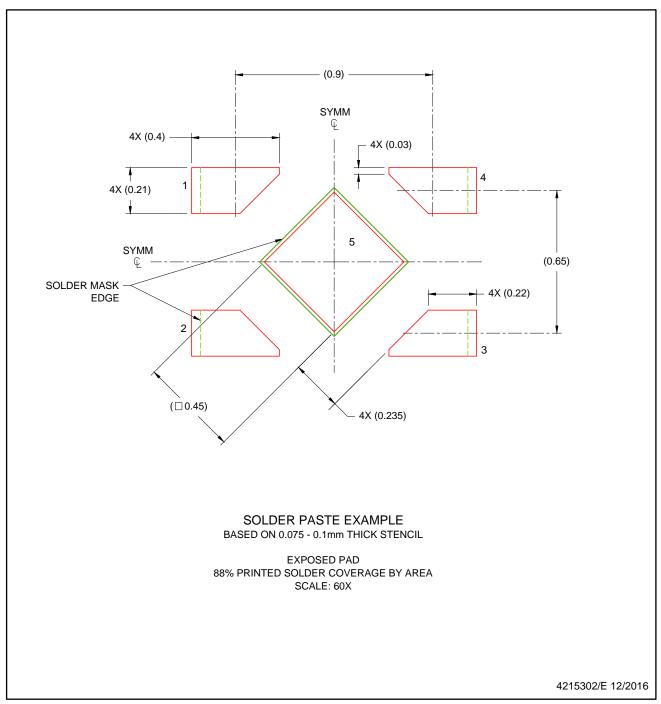

## **EXAMPLE STENCIL DESIGN**

## **DQN0004A**

X2SON - 0.4 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## **PACKAGING INFORMATION**

| Orderable<br>part number | Status (1) | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|--------------------------|------------|---------------|------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TLV743105PDBVR           | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1NGT             |

| TLV74310PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1CCT             |

| TLV74310PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 8U               |

| TLV74311PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DAT             |

| TLV74311PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 8W               |

| TLV74312PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DBT             |

| TLV74312PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 8X               |

| TLV74312PDQNR3           | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 8X               |

| TLV74315PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DCT             |

| TLV74315PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 8Z               |

| TLV74318PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | NIPDAU   SN                   | Level-1-260C-UNLIM         | -40 to 125   | 1D7T             |

| TLV74318PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9A               |

| TLV74318PDQNR3           | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU   NIPDAU               | Level-1-260C-UNLIM         | -40 to 125   | 9A               |

| TLV74325PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DDT             |

| TLV74325PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9B               |

| TLV743285PDBVR           | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DET             |

| TLV743285PDQNR           | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9C               |

| TLV74328PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DFT             |

| TLV74328PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9D               |

| TLV74328PDQNR1           | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU   NIPDAU               | Level-1-260C-UNLIM         | -40 to 125   | 9D               |

| TLV74330PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1DGT             |

| TLV74330PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9E               |

| TLV74333PDBVR            | Active     | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes             | Call TI   Sn   Nipdau         | Level-1-260C-UNLIM         | -40 to 125   | 1CBT             |

| TLV74333PDQNR            | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9F               |

| TLV74333PDQNR3           | Active     | Production    | X2SON (DQN)   4  | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 9F               |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

## PACKAGE OPTION ADDENDUM

7-May-2025

- (2) Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

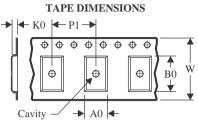

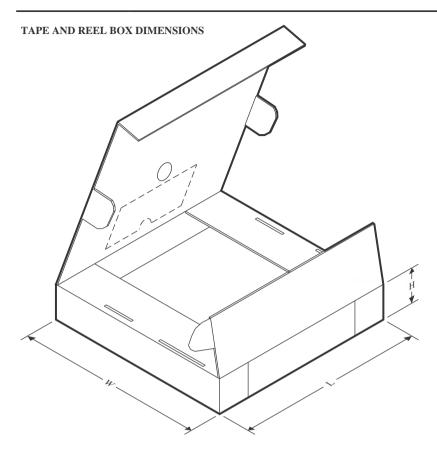

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLV743105PDBVR | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74310PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74310PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74311PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74311PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74312PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74312PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74312PDQNR3 | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q3               |

| TLV74315PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74315PDBVR  | SOT-23          | DBV                | 5    | 3000 | 178.0                    | 9.0                      | 3.3        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74315PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74318PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74318PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74318PDQNR3 | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q3               |

| TLV74325PDBVR  | SOT-23          | DBV                | 5    | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74325PDQNR  | X2SON           | DQN                | 4    | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

# **PACKAGE MATERIALS INFORMATION**

22-Apr-2025

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLV743285PDBVR | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV743285PDQNR | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74328PDBVR  | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74328PDQNR  | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74328PDQNR1 | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q1               |

| TLV74330PDBVR  | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74330PDQNR  | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74333PDBVR  | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TLV74333PDQNR  | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q2               |

| TLV74333PDQNR3 | X2SON           | DQN                | 4 | 3000 | 180.0                    | 8.4                      | 1.16       | 1.16       | 0.5        | 4.0        | 8.0       | Q3               |

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV743105PDBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74310PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74310PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74311PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74311PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74312PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74312PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74312PDQNR3 | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74315PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74315PDBVR  | SOT-23       | DBV             | 5    | 3000 | 180.0       | 180.0      | 18.0        |

| TLV74315PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74318PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74318PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74318PDQNR3 | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74325PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74325PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV743285PDBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV743285PDQNR | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

22-Apr-2025

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV74328PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74328PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74328PDQNR1 | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74330PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74330PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74333PDBVR  | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74333PDQNR  | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

| TLV74333PDQNR3 | X2SON        | DQN             | 4    | 3000 | 210.0       | 185.0      | 35.0        |

SMALL OUTLINE TRANSISTOR

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

<sup>9.</sup> Board assembly site may have different recommendations for stencil design.

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2.

- This drawing is subject to change without notice.

The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

- Features may not exist. Recommend use of pin 1 marking on top of package for orientation purposes.

- Shape of exposed side leads may differ.

- Number and location of exposed tie bars may vary.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 7. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 8. If any vias are implemented, it is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate

design recommendations.