Octal D type transparent latch; 3 state,74AHC573XS20G Replace 74AHC573PW

CROSS

FEATURES

• Wide supply voltage range from 2.0 V to 5.5 V

• Balanced propagation delays

• All inputs have Schmitt-trigger action

• Overvoltage tolerant inputs to 5.5 V

• High noise immunity

• CMOS low power dissipation

• Common 3-state output enable input

• Functionally identical to the 74AHC373; 74AHCT373

• nput levels:

• For 74AHC573: CMOS input level

• For 74AHCT573: TTL input level

• ESD protection:

• HBM JESD22-A114F exceeds 2000 V

• MM JESD22-A115-A exceeds 200 V

• CDM JESD22-C101E exceeds 1000 V

• Latch-up performance exceeds 100

mA per JESD 78 Class II Level A

• Multiple package options

• Specified from -40 °C to +85 °C and

from -40 °C to +125 °C

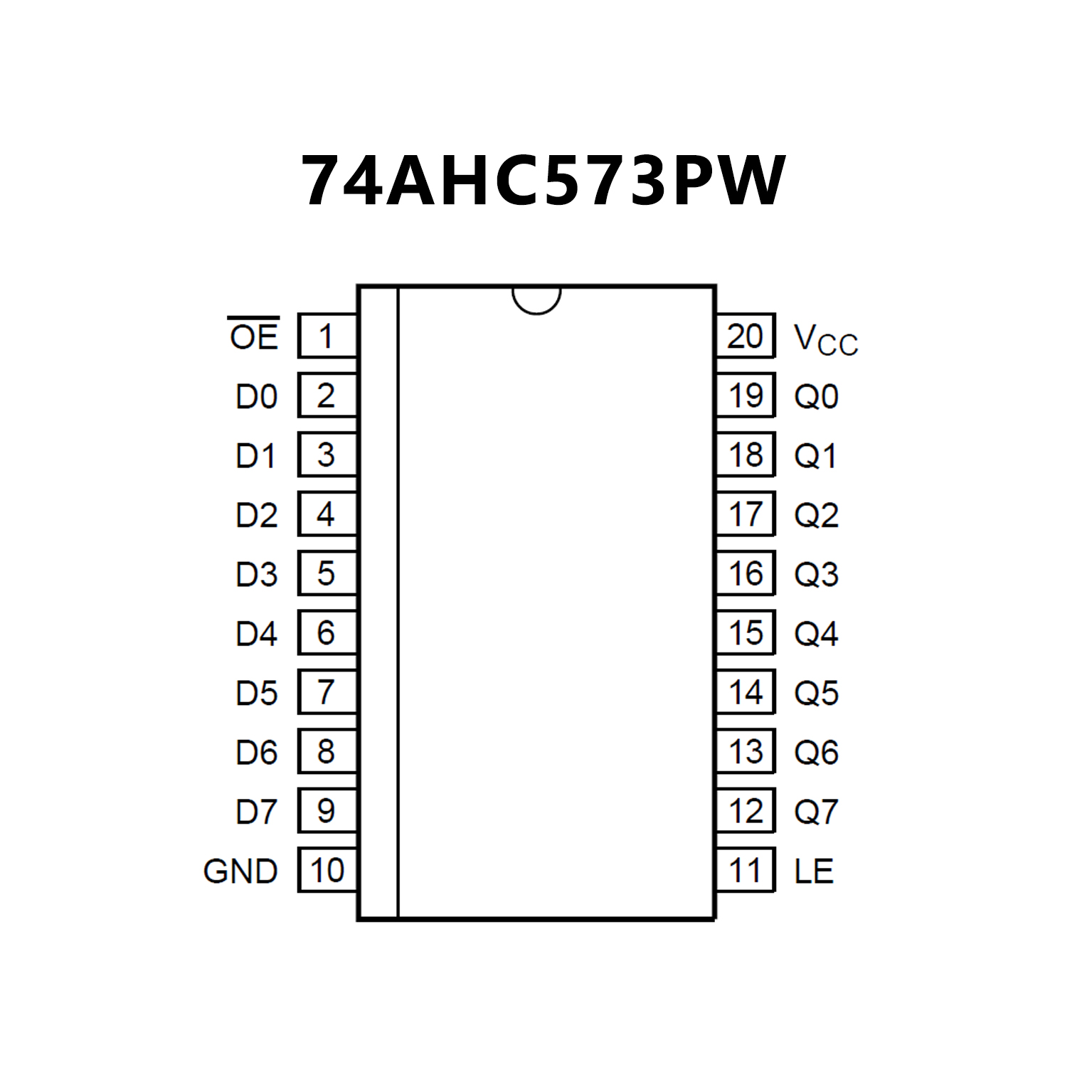

PIN CONFIGUTION

74AHC573XTS20G.pdf

74AHC573XTS20G.pdf