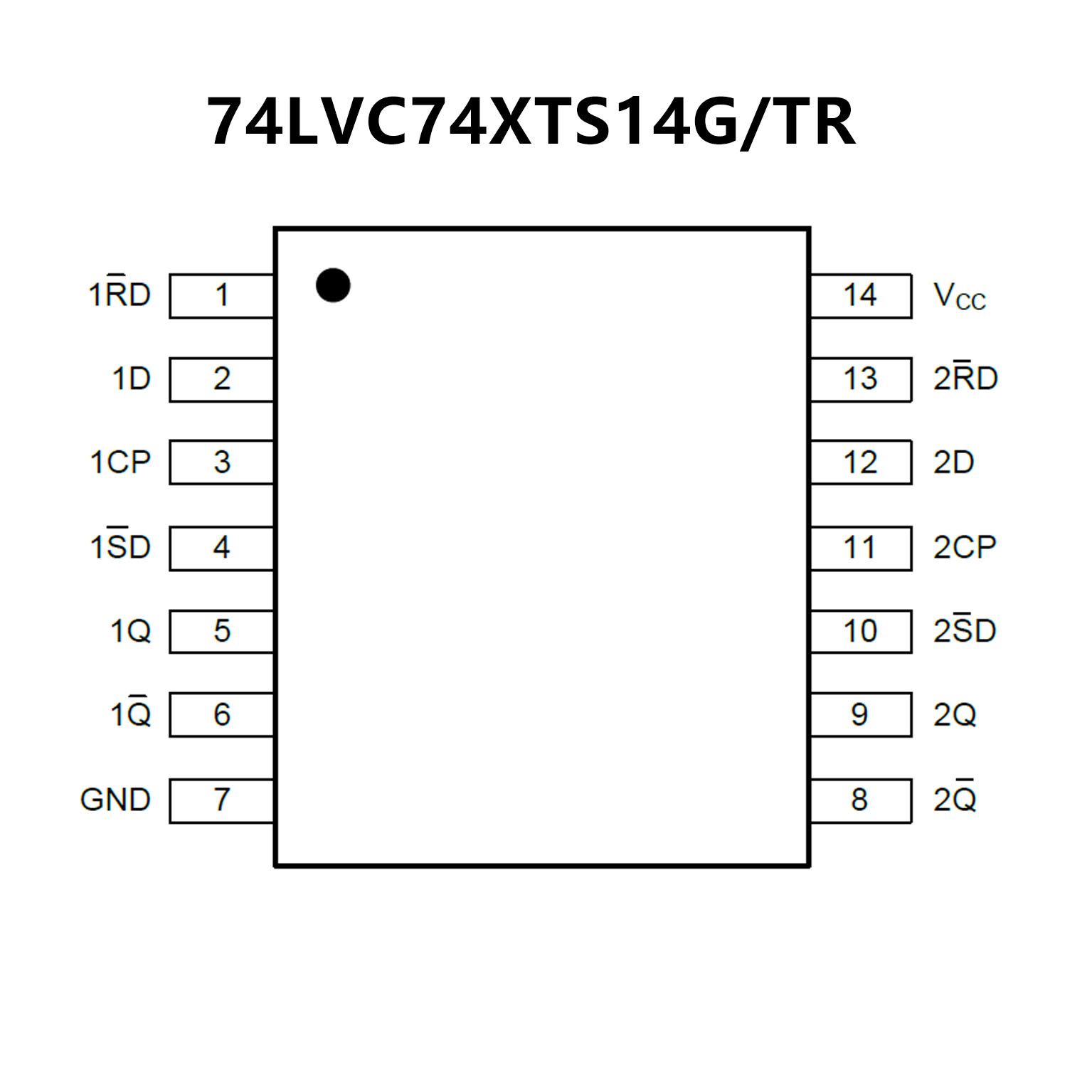

74LVC74XTS14GTR.pdf

74LVC74XTS14GTR.pdf• 5V Tolerant Inputs for Interfacing with 5V Logic

• Wide Supply Voltage Range: 1.2V to 3.6V

• CMOS Low Power Consumption

• Direct Interface with TTL Levels

• -40℃ to +125℃ Operating Temperature Range

• Available in a Green TSSOP-14 Package

• Wide supply voltage range from 2.0 to 6.0 V

• CMOS low power dissipation

• High noise immunity

• Input levels:

• For 74HC74: CMOS level

• For 74HCT74: TTL level

• Symmetrical output impedance

• High noise immunity

• Balanced propagation delays

• Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

• Complies with JEDEC standards:

• JESD8C (2.7 V to 3.6 V)

• JESD7A (2.0 V to 6.0 V)

• ESD protection:

• HBM JESD22-A114F exceeds 2000 V

• MM JESD22-A115-A exceeds 200 V

• Multiple package options

• Specified from -40 °C to +85 °C and from -40 °C to +125 °C