EUP7998.pdf

EUP7998.pdf• VLDOIN Input Voltage Range: 1.1V to 3.5V

• VIN Input Voltage Range: 2.375V to 5.5V

• Typically 3×10μF MLCCs stable for DDR

• Fast Load-Transient Response

• ±10mA Buffered Reference (REFOUT)

• Meet DDR, DDR2 JEDEC Specifications.

Supports DDR3 and Low-Power DDR3/DDR4

VTT Applications

• Power-Good Window Comparator

• With Soft Start, UVLO and OCP

• Thermal Shutdown

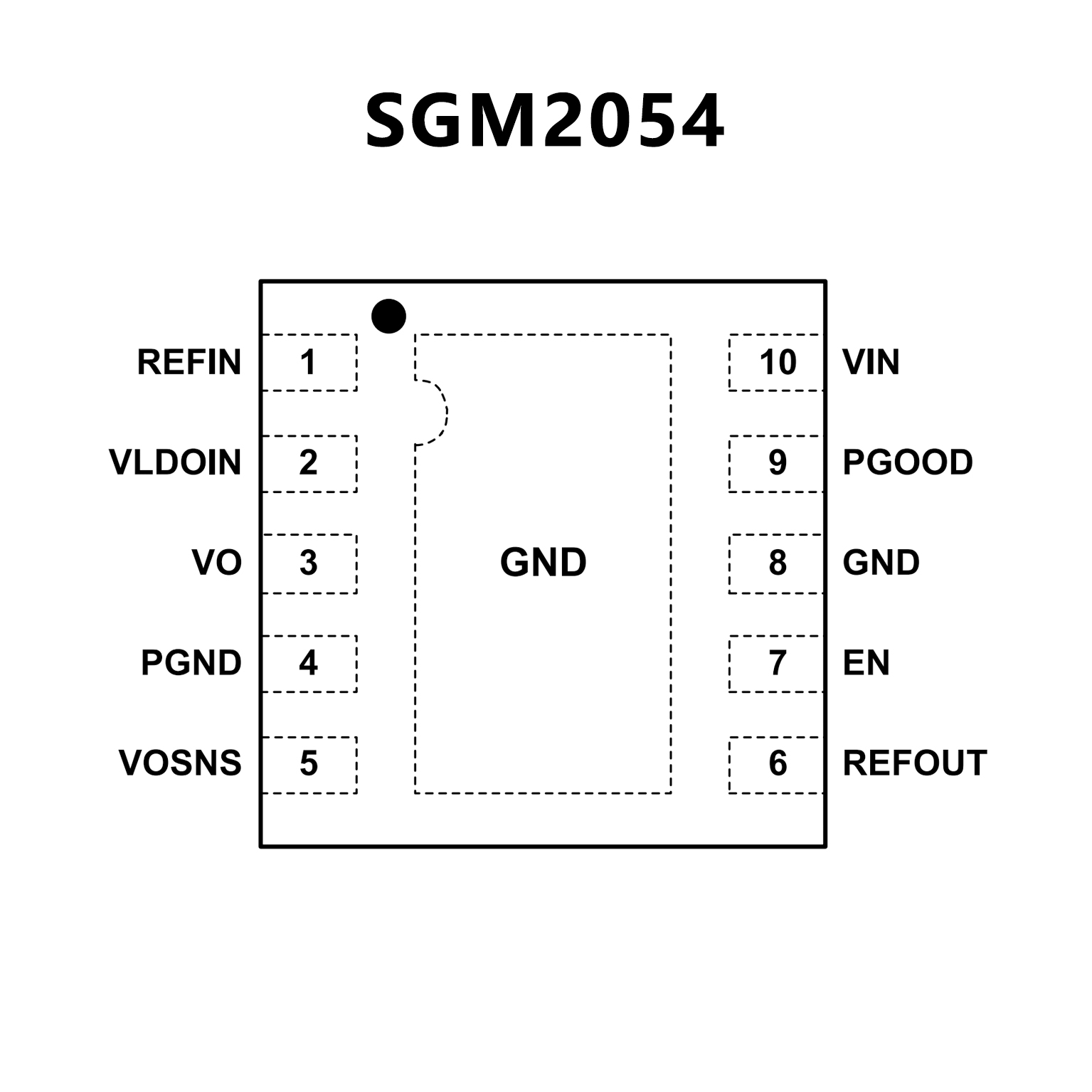

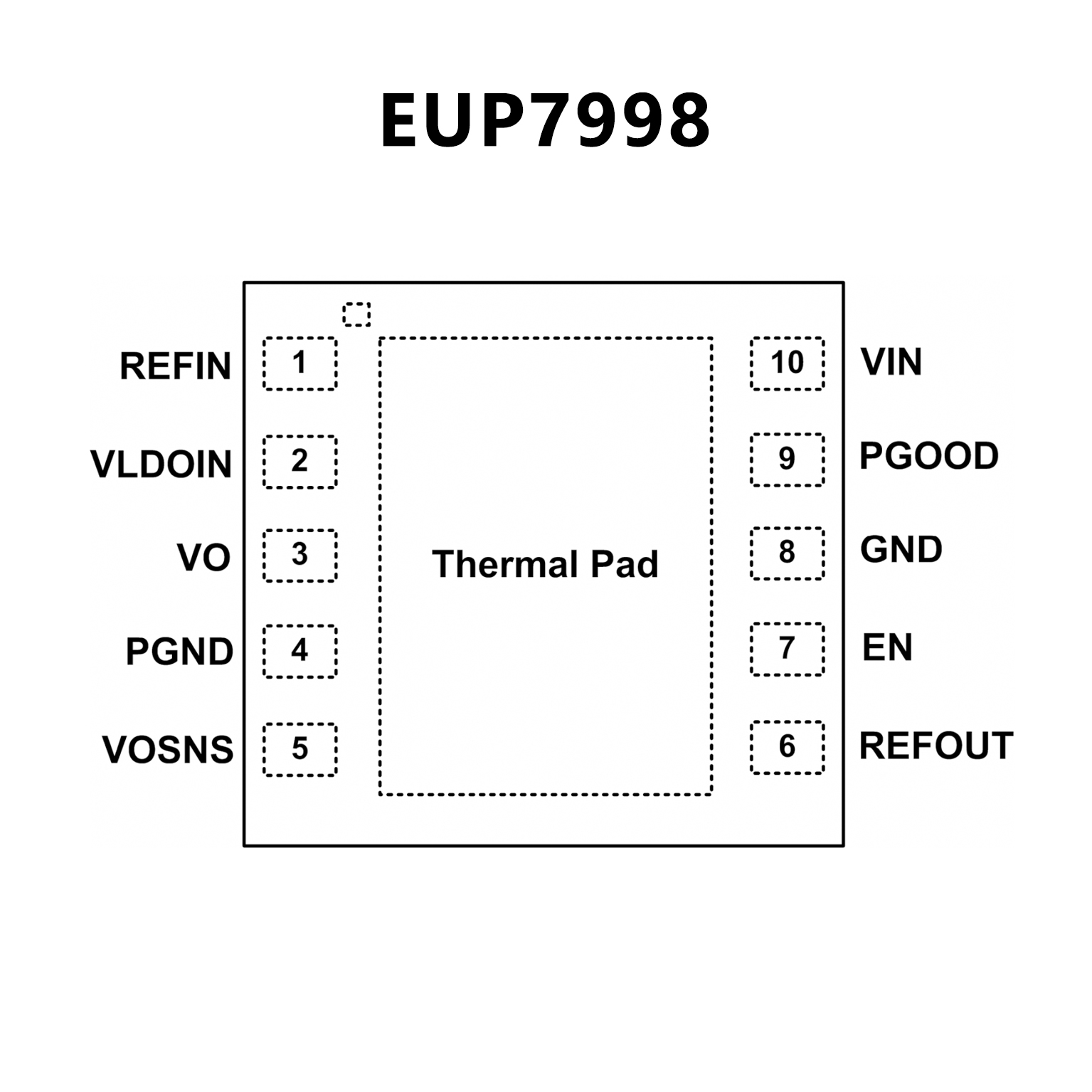

• Available in 10-Pin 3mm×3mm TDFN and

SOP-8 (EP) packages

• RoHS Compliant and 100% Lead(Pb)-Free

Halogen-Free

• VLDOIN Voltage Range: 1.1V to 3.5V

• Low Input Voltages: 2.5V Rail and 3.3V Rail

• Minimum VO Effective Capacitance: 20μF

• Open-Drain Power-Good (PG) Output

• EN Logic Control

• Buffered Reference: ±10mA

• Soft-Start Inrush Control

• Remote Sensing

• Fast Load Transient Response

• Under-Voltage Lockout

• Output Current Limit

• Thermal Shutdown Protection

• -40℃ to +125℃ Operating

Temperature Range

• Available in a Green

TDFN-3×3-10L Package