PI7C9X110BNBE.pdf

PI7C9X110BNBE.pdf

No.11342

● Compliant with Advanced Configuration and Power Interface

Specification (ACPI), Revision 2.0b

● Compliant with System Management (SM) Bus, Version 2.0

● Forward bridging (PCI Express as primary bus, PCI as secondary

bus)

● Reverse bridging (PCI as primary bus, PCI Express as secondary

bus)

● Transparent mode support

● Non-transparent mode Support

● GPIO support (4 bi-directional pins)

● Power Management (including ACPI, CLKRUN_L, PCI_PM)

● Masquerade Mode (pre-loadable vendor, device, and revision IDs)

● EEPROM (I2C) Interface

● SM Bus Interface

● Auxiliary powers (VAUX, VDDAUX, VDDCAUX) support

● Power consumption at about 1.0 Watt in typical condition

● Extended commercial/industrial temperature range (-40C to 85C)

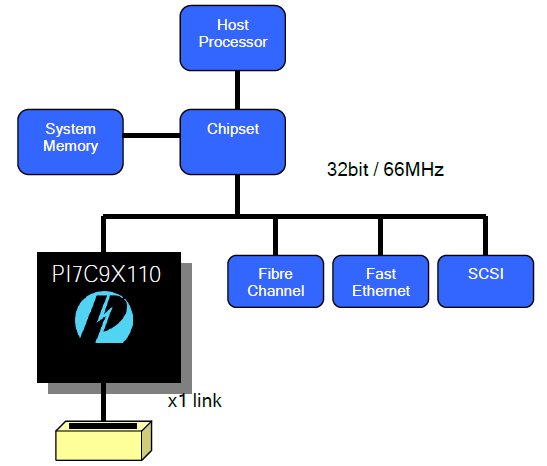

PI7C9X110 is a PCIe-to-PCI bridge. PI7C9X110 is compliant with the PCI Express Base Specification, Revision 1.0a, the PCI Express Card Electromechanical Specification, Revision 1.0a, the PCI Local Bus Specification, Revision 3.0 and PCI Express to PCI Bridge Specification, Revision 1.0. PI7C9X110 supports transparent and non-transparent mode of operations. Also, PI7C9X110B supports forward and reverse bridging. In forward bridge mode, PI7C9X110 has an x1 PCI Express upstream port and a 32-bit PCI downstream port. The 32-bit PCI downstream port is 66MHz capable (see figure 1-1). In reverse bridge mode, PI7C9X110 has a 32-bit PCI upstream port and an x1 PCI Express downstream port. PI7C9X110 configuration registers are backward compatible with existing PCI bridge software and firmware. No modification of PCI bridge software and firmware is needed for the original operation. The PCIe port of the PI7C9X110 bridge always has higher priority over the PCI ports if the configuration registers are accessed simultaneously via the PCIe and PCI ports.